Obsah:

- Krok 1: Sestavení modulu PWM- zdrojový soubor

- Krok 2: Sestavení modulu PWM- nastavení Vivado

- Krok 3: Sestavení modulu PWM- vytvořte soubor projektu

- Krok 4: Budování modulu PWM- návrh bloku bloku a nastavení souboru omezení (I)

- Krok 5: Budování modulu PWM- návrh bloku bloku a nastavení souboru omezení (II)

- Krok 6: Budování modulu PWM- návrh bloku bloku a nastavení souboru omezení (III)

- Krok 7: Sestavení modulu PWM- návrh bloku bloku a nastavení souboru omezení (IV)

- Krok 8: Sestavení modulu PWM- návrh bloku a nastavení souboru omezení (V)

- Krok 9: Sestavení modulu PWM- instalace hardwaru

- Krok 10: Sestavení modulu PWM- generujte bitstream a spusťte SDK

- Krok 11: Sestavení modulu PWM- vytvořte novou aplikaci v sadě Xilinx SDK

- Krok 12: Sestavení modulu PWM- přehled Průzkumníka projektů (I)

- Krok 13: Sestavení modulu PWM- přehled Průzkumníka projektů (II)

- Krok 14: Sestavení modulu PWM- přehled Průzkumníka projektů (III)

- Krok 15: Sestavení modulu PWM- zabalení funkce PWM (I)

- Krok 16: Sestavení modulu PWM- zabalení funkce PWM (II)

- Krok 17: Sestavení modulu PWM- zabalení funkce PWM (III)

- Krok 18: Sestavení modulu PWM- nechte jej běžet

- Krok 19: Streamování zpracování videa na Digilent ZYBO s OV7670

- Krok 20: Dokončete blokový diagram

- Krok 21: Připojte OV7670 k ZYBO

- Krok 22: Vytvořte návrh bloku

- Krok 23: Přidejte soubory VHDL pro ovládání a zachycení kamery OV7670

- Krok 24: Přidejte soubor omezení

- Krok 25: Přidejte IP Repo pro HLS IP

- Krok 26: Přidejte moduly a IP

- Krok 27: Nastavení konfigurace IP

- Krok 28: Přidejte a nakonfigurujte blok PS IP

- Krok 29: Část 1. Sestavení modulu PWM pro servomotory

- Krok 30: Připojení bočního vstupu videa (zvýrazněno)

- Krok 31: Připojení k OV7670

- Krok 32: Připojení na straně výstupu videa

- Krok 33: Spusťte blokování a automatizaci připojení

- Krok 34: Vygenerujte HDL Wrapper

- Krok 35: Generujte bitstream, exportujte hardware do SDK, spusťte SDK z Vivado

- Krok 36: SDK (bez FreeRTOS)

- Krok 37: Implementace FreeRTOS

- Krok 38: Pokyny k použití

- Krok 39: Reference a odkazy

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:24.

- Naposledy změněno 2025-01-23 14:38.

Začněte v prvním kroku, kde najdete podrobnosti o pouhém vytvoření 2osého servopohonu PWM.

Začněte u masivního blokového diagramu (krok 19) pro celý projekt.

Použili jsme nastavení kamery + posunu/naklonění:

Pro připojení serva byl použit PmodCON3 od společnosti Digilent.

Krok 1: Sestavení modulu PWM- zdrojový soubor

Krok 2: Sestavení modulu PWM- nastavení Vivado

Nejprve si stáhněte Vivado Design Suite z webu Xilinx. Nainstalujte si celou sadu návrhů, včetně sady Vivado Software Development Kit (SDK). Tento projekt používá verzi 2017.2.

Mezitím by měl být také nainstalován Digilent Adept 2 jako ovladač desky Zybo.

Krok 3: Sestavení modulu PWM- vytvořte soubor projektu

Před vytvořením souboru projektu byste se měli ujistit, že jste již správně nainstalovali soubor Zybo jako tutoriál zde:

Instalace souboru Vivado verze 2015.1 a novější

Otevřete Vivado 2017.2. Na rychlém startu klikněte na Vytvořit projekt -> Další -> Název projektu (zde pojmenujte název projektu) -> Typ projektu. Na Typ projektu vyberte Projekt RTL a označte „Nezadávejte v tuto chvíli zdroje“. Dále ve Výchozí části vyberte jako zobrazované jméno „Desky“a „Zybo“. Dále klikněte na Dokončit pro spuštění projektu.

Krok 4: Budování modulu PWM- návrh bloku bloku a nastavení souboru omezení (I)

V aplikaci Flow Navigator klikněte na „“Vytvořit návrh bloku”a poté stiskněte OK. kliknutím na znaménko „+“přidáte potřebné IP adresy. Přidat:

- Jeden systém zpracování ZYNQ7 Dva časovače AXI

- Dva časovače AXI

Krok 5: Budování modulu PWM- návrh bloku bloku a nastavení souboru omezení (II)

Po přidání IP spusťte automatizaci bloků a automatizaci připojení. Jakmile je automatizace dokončena, v bloku „axi_timer_0“klikněte pravým tlačítkem na pwm0 -> Vytvořit externí. Pojmenujte externí pin pwm0 jako pwm_Xaxis. Výše uvedený postup také opakujte na bloku „axi_timer_1“a pojmenujte externí pin pwm0 jako pwm_Zaxis.

Krok 6: Budování modulu PWM- návrh bloku bloku a nastavení souboru omezení (III)

Všimněte si, že pokaždé, když dokončíme Block Design ve Vivado, musíme vytvořit HDL Wrapper. Protože to bude modul nejvyšší úrovně pro každý projekt.

Krok 7: Sestavení modulu PWM- návrh bloku bloku a nastavení souboru omezení (IV)

Nyní musíme nastavit náš soubor omezení pro přiřazení pinů připojených k našemu blokovému diagramu. Zavřete okno Návrh bloku, na kartě Zdroje „Přidat zdroje“-> Přidat nebo vytvořit omezení-> přidat Zybo-Master.xdc jako naše soubory omezení.

Krok 8: Sestavení modulu PWM- návrh bloku a nastavení souboru omezení (V)

Otevřete soubor omezení Zybo-Master.xdc ze složky Omezení, odkomentujte porty, které chceme specifikovat jako výstupní signály, a přejmenujte „get_ports {XXXX}“, což XXXX označuje externí pin pojmenovaný v blokovém diagramu. Nastavení souboru omezení je znázorněno na obrázku.

Krok 9: Sestavení modulu PWM- instalace hardwaru

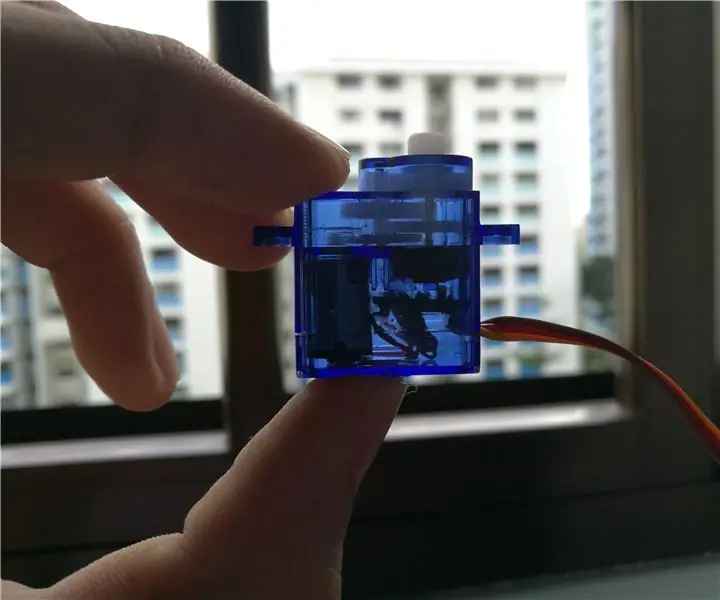

Připojte servomotory k Pmod CON3. TowerPro SG90 je model servomotoru, který jsme použili v tomto projektu. U vodičů servomotoru představuje oranžový vodič signál PWM připojený ke kolíku SIG v Pmod CON3. Červený vodič Vcc je napájecí vodič připojený k kolíku VS v Pmod CON3. Nakonec je hnědý vodič Gnd uzemňovací vodič připojený ke kolíku GND. Dále vložte Pmod CON3 do horní řady portu JD v desce Zybo.

Krok 10: Sestavení modulu PWM- generujte bitstream a spusťte SDK

1. Na kartě Project Navigator spusťte Generate BitStream.

2. Exportujte hardware: Soubor> Exportovat> Exportovat hardware-> označit „zahrnout bitstream“-> OK 3. Spustit SDK: Soubor-> Spustit SDK.

Krok 11: Sestavení modulu PWM- vytvořte novou aplikaci v sadě Xilinx SDK

Vytvořte novou aplikaci:

Soubor> Nový> Projekt aplikace -> Zadejte název projektu -> Dokončit

V části Project Explorer by měly existovat tři složky.

V tomto případě je „design_1_wrapper_hw_platform_0“složka, kterou dříve exportoval Vivado. Axis_2_PWM_SDK_bsp je složka balíčku podpory desky. A Axis_2_PWM_SDK je naše hlavní složka projektu v SDK. Soubor „helloworld.c“můžete vidět ve složce „src“v Axis_2_PWM_SDK, kde je „helloworld.c“hlavním souborem.

Krok 12: Sestavení modulu PWM- přehled Průzkumníka projektů (I)

Pojďme zkontrolovat některé soubory v aplikaci Project Explorer. Nejprve ve složce „design_1_wrapper_hw_platform_0“otevřete soubor „system.hdf“. Tento soubor ukazuje mapu adres pro procesor ps7_cortex9 a bloky IP přítomné v našem návrhu.

Krok 13: Sestavení modulu PWM- přehled Průzkumníka projektů (II)

Poté zkontrolujte soubor „include“a „libsrc“ve složce „Axis_2_PWM_SDK_bsp“. Soubory knihovny nám zde umožňují interakci s hardwarovými periferiemi bez „hraní“registrů.

Krok 14: Sestavení modulu PWM- přehled Průzkumníka projektů (III)

Prostřednictvím dokumentace BSP je xtmrctr.h nalezen jako Xilinx Timer Control Library související s AXI Timer. Typicky bychom zde mohli najít požadovanou funkci PWM. Pokud si však přečtete dokumentaci „tmrctr_v4_3“, ukáže se, že ovladač aktuálně nepodporuje provoz PWM zařízení. Kvůli nedostatku funkce PWM musíme zabalit naši funkci PWM pomocí xtmrctr.h a AXI Timer v2.0 LogiCORE IP Product Guide.

Krok 15: Sestavení modulu PWM- zabalení funkce PWM (I)

Zpět na hlavní soubor „helloworld.c“zahrňte následující soubory záhlaví:

Krok 16: Sestavení modulu PWM- zabalení funkce PWM (II)

Definujte základní adresy dvou AXI TImer prostřednictvím „xparameters.h“.

Krok 17: Sestavení modulu PWM- zabalení funkce PWM (III)

Vytvořte požadovanou funkci PWM.

Duty_val: převádí hodnotu stupně na pracovní cyklus. PWM_Freq_Duty: nastavte požadovanou frekvenci a pracovní cyklus pro generování PWM. Rovněž by mělo být přiřazeno časové období.

PWM_START: přiřaďte adresu registru PWM a začněte generovat PWM.

PWM_STOP: přiřaďte adresu registru PWM a zastavte generování PWM.

Zbytek demo kódu je uveden v „helloworld.c“pod „Axis_2_PWM_SDK“

Krok 18: Sestavení modulu PWM- nechte jej běžet

1. Naprogramujte FPGA pomocí SDK

- Připojte Zybo Board přes USB port k PC.

- Nástroje Xilinx -> Programovat FPGA

2. Spusťte program

Klikněte na ikonu „Spustit“a rozbalte nabídku -> Spustit jako -> Spustit na hardwaru

3. Terminál SDK

- Otevřete terminál SDK -> Připojit k sériovému portu -> OK

- Spusťte program. Pokud se demo kód úspěšně spustí, měli byste vidět „Inicializace dokončena!“na terminálu SDK.

Krok 19: Streamování zpracování videa na Digilent ZYBO s OV7670

Kompletní archivní soubor přiložen.

Krok 20: Dokončete blokový diagram

Toto ukazuje kompletní schéma všech připojení a IP bloků v projektu

Krok 21: Připojte OV7670 k ZYBO

Vytvořte připojení k propojení modulu ov7670 se ZYBO Pmods

Data Pmod je Pmod D

Ovládací Pmod je Pmod C

Navíc připojte PmodCON3 a serva, jak je uvedeno v první polovině tohoto tutoriálu

Krok 22: Vytvořte návrh bloku

V aplikaci Flow Navigator klikněte na „Vytvořit návrh bloku“a poté stiskněte OK.

Krok 23: Přidejte soubory VHDL pro ovládání a zachycení kamery OV7670

Přidejte do projektu soubory VHDL připojené k tomuto kroku

Krok 24: Přidejte soubor omezení

Přidejte do projektu připojený soubor omezení.

Krok 25: Přidejte IP Repo pro HLS IP

Vezměte připojený soubor Zip a rozbalte jej do nové složky s podobným názvem v novém adresáři (složce) s názvem „HLS_repo“.

Přidejte do svého projektu úložiště IP tak, že přejdete do katalogu IP a pravým tlačítkem myši vyberete „Přidat úložiště…“

Přejděte do adresáře „HLS_repo“a vyberte jej.

Volitelné: Vytvořte si blok zpracování videa HLS pro sebe!

Krok 26: Přidejte moduly a IP

Přidejte moduly ov7670_axi_stream_capture, debounce a ov7670_controller do blokového diagramu kliknutím pravým tlačítkem na pozadí a výběrem „Přidat modul…“

Podobně přidejte IP:

- HLS_Video_Track

- Zápis do vyrovnávací paměti video rámečku

- Čtení vyrovnávací paměti video rámečku

- Ovladač časování videa

- Výstup AXI4-Stream na video

- 3 „Plátek“

- Konstantní

- 2 časovače AXI

Krok 27: Nastavení konfigurace IP

Jak je vidět na obrázcích

Krok 28: Přidejte a nakonfigurujte blok PS IP

Přidejte procesní systém ZYNQ7 do blokového diagramu

upravit konfiguraci:

-

Konfigurace PS-PL

-

HP

- Povolit S HP 0

- Povolit S HP 1

-

-

Konfigurace hodin

-

Látkové hodiny PL

- FCLK_0 na 100 MHz

- FCLK_1 při 25 MHz (výstupní hodiny)

- FLCK_2 při 35 MHz (<= 50 MHz) (CameraClock)

-

Krok 29: Část 1. Sestavení modulu PWM pro servomotory

Vyveďte axi_timer_0 pwm0 na nový výstupní port pwm_Xaxis

Vyveďte axi_timer_1 pwm0 na nový výstupní port pwm_Zaxis

Krok 30: Připojení bočního vstupu videa (zvýrazněno)

Správně připojte IP bloky na straně vstupu videa

(* tato připojení by měla být vytvořena výběrem správných možností během automatizace připojení) „aclk“z axi_stream_capture přejde na:

- ap_clk na zápis do vyrovnávací paměti rámce videa

- ap_clk na bloku zpracování video streamu HLS

- *aclk na AXI smartconnect IP z vyrovnávací paměti video rámečku Zápis do S_AXI_HP0

- *aclk odpovídající kanálům AXI Interconnect IP pro kanály S_AXI bloku zpracování videa HLS a vyrovnávací paměť rámce video zápisu S_AXI_HP0_ACLK na blok PS

Signál video streamu je jednoduše zapojen do série od sběrného bloku k paměťovému rozhraní Zynq.

- Video přechází z bloku záznamu do bloku zpracování HLS.

- Zpracované video z bloku HLS jde do bloku pro zápis do vyrovnávací paměti rámců.

- *Blok pro zápis do vyrovnávací paměti rámců se připojuje k rozhraní HP0 v bloku Zynq PS.

- Signál m_axis_tuser z výstupu zachycovacího bloku je ručně zapojen jak do vstupního signálu video_in_TUSER na zpracovatelském bloku HLS, tak do signálu ap_start na stejném bloku.

Signál TUSER (tuser) používá protokol toku videa AXI k označení začátku rámce videa. AP_Start říká bloku HLS, aby zahájil zpracování. Používáme tedy tuser ke spuštění bloku HLS ke zpracování každého snímku tak, jak přichází. Při připojování jediného signálu sběrnice a jeho rozdělování tímto způsobem je nutné jej také připojit k normálnímu koncovému bodu zbytku sběrnice. Vivado předpokládá, že pokud připojujete signál ručně, chcete odpojit to, k čemu by se normálně připojoval.

Konfigurační nastavení IP bloků:

Zápis do vyrovnávací paměti video rámečku:

Formáty videa: RGB8

1 vzorek za hodiny Max. Sloupce: 1280 (> = 640) Max. Řádky: 960 (> = 480) Max. Šířka dat: 8

Krok 31: Připojení k OV7670

Na bloku ov7670_axi_stream_capture

- Vytvořte všechny vstupy externí (klikněte pravým tlačítkem na špendlík a vyberte z nabídky nebo klikněte levým tlačítkem-> ctrl+T)

- Nechte jména tak, jak jsou

Na bloku ov7670_controller

- Všechny externí výstupy bloku nastavte na externí

- Přejmenujte port config_finished na led0

- připojte clk k CameraClock (<= 50MHz) (FCLK_2)

Na debounce bloku

- připojte vstup button1 k externímu vstupnímu portu s názvem btn0

- připojte out1 k řádku pro opětovné odeslání na bloku IP ov7670_controller

- připojte vstup button2 k externímu vstupnímu portu s názvem btn3

- připojte out2n ke vstupu ext_reset_in na Reset IP systému procesoru pro hodinovou doménu záznamu videa. (*To může být nutné provést po vygenerování této IP*)

- připojte clk k CameraClock (<= 50MHz) (FCLK_2)

Krok 32: Připojení na straně výstupu videa

Připojení pro bloky Video Timing Controller (VTC), AXI4-Stream na video výstup a řezy

- Pro vid_io_out_clk a VTC clk použijte hodiny 25 MHz (FCLK_1)

- Použijte 100MHz hodiny (FCLK_0) pro aclk na výstupu AXI4-Stream

- vtiming_out na vtiming_in

- Vyrovnávací paměť pro čtení rámečku videa m_axis_video přejde na AXI4-Stream a výstup videa video_in

- vtg_ce jde do gen_clken

- Vazba VTC clken, aclken, vid_io_out_ce na konstantní dout [0: 0]

- Přeneste vid_hsync a vid_vsync na externí výstupní porty vga_hs a vga_vs. (bez obrázku)

Plátky:

-

Plátky by měly být nastaveny podle přiložených obrázků

- přejmenujte bloky na slice_red, slice_green a slice_blue

- nastavte rozsahy řezů, jak je znázorněno na obrázcích, podle názvu bloku

- připojte každý výstup výřezu k výstupu externího portu, jak je znázorněno na obrázku.

- vid_data [23: 0] se připojuje ke vstupům pro každý řez (Din [23: 0])

Krok 33: Spusťte blokování a automatizaci připojení

Spusťte Block Automation a připojte věci z bloku ZYNQ7 PS. Jak ukazuje obrázek.

Spusťte automatizaci připojení a vytvořte všechny propojovací IP. Věnujte pozornost všem možnostem na každém obrázku.

V bloku debounce připojte out2n ke vstupu hodinové domény pro záznam videa Procesor Reset systému ext_reset_in.

Krok 34: Vygenerujte HDL Wrapper

Vytvořte obal HDL pro svůj návrh bloku.

Nastavte jej jako horní modul.

Krok 35: Generujte bitstream, exportujte hardware do SDK, spusťte SDK z Vivado

Do exportu nezapomeňte zahrnout bitový tok.

Generování bitového toku může trvat velmi dlouho.

Poté spusťte SDK

Krok 36: SDK (bez FreeRTOS)

Tato verze dělá vše bez použití FreeRTOS a pěkně kondenzuje kód.

Vytvořte samostatný BSP na základě návrhu hardwaru. Výchozí možnosti by měly být v pořádku. Ujistěte se, že byly vygenerovány zdroje BSP.

Vytvořte aplikaci podle obrázku. (prázdná aplikace)

Odstraňte automaticky generovaný hlavní soubor a importujte připojené soubory.

Krok 37: Implementace FreeRTOS

Tato verze používá FreeRTOS. Vytvořte FreeRTOS901 BSP na základě návrhu hardwaru. Výchozí možnosti by měly být v pořádku. Ujistěte se, že byly vygenerovány zdroje BSP.

Vytvořte aplikaci podle obrázku. (prázdná aplikace)

Odstraňte automaticky generovaný hlavní soubor a importujte připojené soubory.

Krok 38: Pokyny k použití

Spustit tento projekt je trochu ošidné. Postupujte podle uvedených pokynů.

Po zapnutí se ujistěte, že váš ZYBO nic nenačítá. To znamená, že by se kontrolka Hotovo neměla rozsvítit. Jedním ze způsobů, jak toho dosáhnout, je nastavit propojku zdroje spouštění na JTAG.

Otevřete projekt (FreeRTOS nebo ne), který chcete programovat ze sady SDK

- Zapněte ZYBO. Kontrolka Hotovo by se neměla rozsvítit.

- Naprogramujte FPGA pomocí bitového souboru. Kontrolka Hotovo by se měla rozsvítit. LED0 by se neměla rozsvítit.

- Spusťte kód (nezapomeňte jít za počáteční zarážku, pokud to děláte).

V tomto okamžiku byste měli získat výstup na displeji VGA.

Restartování (pokud dojde k chybě nebo cokoli jiného): rychle klepněte na tlačítko PS-SRST nebo vypněte a znovu zapněte ZYBO. Pokračujte od kroku 2.

Zastavení procesoru pomocí debuggeru způsobí, že kamera místo pohybu bude držet pozici. Stream videa bude i tak pokračovat.

Krok 39: Reference a odkazy

Referenční příručky a dokumentace Xilinx:

- PG044 - AXI -stream na video výstup

- PG278 - vyrovnávací paměť pro čtení/zápis obrazového rámečku videa

Další odkazy:

- Lauriin blog - vstup VDMA

- Lauriho blog - výstup OV7670 na VGA pomocí BRAM

- Hamsterworks wiki, Mike Fields, původní zdroj kódu OV7670

- Datový list zobrazující základní specifikace časování

Doporučuje:

Kamera s dálkovým ovládáním od Raspberry Pi: 5 kroků (s obrázky)

Kamera pro dálkové ovládání od Raspberry Pi: Tento návod vás provede následujícími kroky: 1. Umístěte kameru na místní web (pro vzdálené vidění přes počítač nebo telefon) 2. Ovládání kamerového vidění (pomocí převodového motoru) Seznam dílů pro projekt: 1. Motor s převodovkou https://amzn.to/2OLQxxq2. Raspberry Pi B https: //amzn.to

Mechanismus otáčení a naklápění pro časové intervaly DSLR: 7 kroků (s obrázky)

Mechanismus otáčení a naklánění pro časosběrné snímání DSLR: Měl jsem několik krokových motorů a opravdu jsem je chtěl použít k vytvoření něčeho skvělého. Rozhodl jsem se, že pro svou kameru DSLR udělám systém Pan and Tilt, abych mohl vytvářet skvělé časové prodlevy. Věci, které budete potřebovat: 2x krokové motory -htt

Jak upravit mikro servomotor (SG90) pro nepřetržité otáčení: 6 kroků (s obrázky)

Jak upravit mikro servomotor (SG90) pro kontinuální otáčení: Ach ne! Došly mi stejnosměrné motory! Máte kolem sebe náhradní serva a rezistory? Pak to upravme! Normální servo se otáčí asi o 180 stupňů. Očividně jej nemůžeme použít pro vozidlo běžící na kolech. V tomto tutoriálu půjdu

Upravte servo Hitec Hs-325 pro nepřetržité otáčení: 3 kroky (s obrázky)

Upravte servo Hitec Hs-325 pro nepřetržité otáčení: Servomotory jsou navrženy tak, aby se mohly otáčet maximálně +/- 130 stupňů. Lze je však snadno upravit tak, aby se otáčelo o 360 stupňů. Hack je velmi dobře zdokumentován pro různé modely servomotorů. Zde používám servo Hitec HS-325HB zakoupené v ServoCity. Th

Jak upravit servomotor pro nepřetržité otáčení (robot s jedním chodítkem): 8 kroků (s obrázky)

Jak upravit servomotor pro nepřetržité otáčení (robot s jedním chodítkem): Tento návod je součástí jednoho chodítka. Https://www.instructables.com/id/How-to-build-the-one-motor- Walker/Vím, že existují biliony tutoriálů, které jsou k dispozici :-) Jsou tam, kde se ve škole během polední přestávky nahrávají fotoaparátem Sony Mavica (disketa