Obsah:

- Krok 1: Konfigurace programovatelné logiky Zynq pro vysílač

- Krok 2: Konfigurace programovatelné logiky Zynq pro přijímač

- Krok 3: Nastavení ovladače VDMA

- Krok 4: Nastavení sítě Nanorouter

- Krok 5: Nastavení systému zpracování Zynq pro přenos dat přes ethernet

- Krok 6: Nastavení systému zpracování Zynq pro příjem dat přes ethernet

- Krok 7: Připojte desky Zybo ke zdroji HDMI a HDMI dřezu

- Krok 8: Alternativní nápady na vylepšení

- Krok 9: Usnadnění

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:22.

- Naposledy změněno 2025-01-23 14:38.

Přáli jste si někdy, abyste mohli svůj televizor připojit k počítači nebo notebooku jako externí monitor, ale nechtěli jste mít v cestě všechny ty otravné kabely? Pokud ano, tento návod je právě pro vás! I když existují některé produkty, které tohoto cíle dosahují, kutilský projekt je mnohem uspokojivější a potenciálně levnější.

Tento koncept se liší od produktů, jako je chromecast, protože je určen k tomu, aby místo streamovacího zařízení nahradil kabel HDMI připojený k monitoru.

Náš projekt byl vytvořen jako závěrečný projekt pro kurz operačních systémů v reálném čase na Kalifornské státní polytechnické univerzitě, San Luis Obispo.

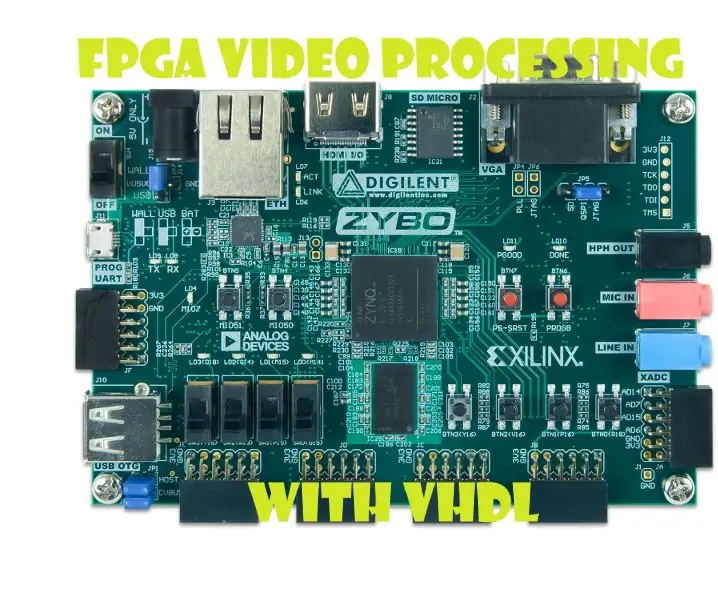

Cílem projektu je využít dvě desky Digilent Zybo, které budou fungovat jako bezdrátové komunikační rozhraní mezi vysílacím zařízením HDMI (PC, blu-ray atd.) A přijímacím zařízením HDMI (stolní monitor, projektor, televize atd.).

Jeden Digilent Zybo bude připojen přes HDMI k vysílacímu zařízení a druhý bude připojen přes HDMI k přijímacímu zařízení.

Bezdrátová komunikace bude probíhat pomocí bezdrátové místní sítě vyhrazené pro vysílač a přijímač, aniž by byla směrována přes domácí router nebo jiné podobné zařízení. Bezdrátovým modulem použitým pro tento projekt je nanoprocesor tplink wr802n, z nichž jeden funguje jako přístupový bod pro vytvoření sítě a druhý jako klient pro připojení k síti. Každý nanorouter bude připojen ethernetovým kabelem k desce Zybo. Po připojení k těmto routerům budou zařízení komunikovat přes TCP, jako by byla připojena jediným ethernetovým kabelem (což znamená, že jedinou konfigurací potřebnou k navázání připojení je IP adresa klienta).

Přestože cílem projektu bylo usnadnit streamování videa s rozlišením 1080 x 720 při 60 Hz, nebylo to dosažitelné kvůli omezením šířky pásma v bezdrátové síti a nedostatku komprese videa v reálném čase za účelem snížení dat potřebných k odeslání. Místo toho tento projekt slouží jako rámec pro budoucí vývoj k dosažení tohoto cíle, protože má výrazně omezená omezení snímkové frekvence pro správné streamování dat HDMI podle očekávání.

Požadavky projektu:

2x vývojové desky Digilent Zybo (musí mít alespoň jeden port HDMI)

2x HDMI kabely

2x microusb kabely (pro připojení Zybo k PC pro vývoj)

2x nanoroutery tplink wr802n (včetně adtl. 2x mikrousb a napájecích adaptérů do zásuvky)

2x ethernetové kabely

*** Poznámka: Tento tutoriál předpokládá seznámení se sadou návrhů Vivado a zkušenost s vytvářením nového projektu a návrhu bloku. ***

Krok 1: Konfigurace programovatelné logiky Zynq pro vysílač

Náš přístup k vývoji programovatelné logiky vysílače spočíval v předání signálu z počítače do počítače pomocí dvou bloků VDMA (Video Direct Memory Access), jednoho pro zápis a jednoho pro čtení.

Oba jsou vybrány pro volně běžící režim 3 vyrovnávací paměti (0-1-2). Protože je jádro videa optimalizováno na 60 snímků za sekundu, znamená to, že VDMA bude zapisovat nebo číst do nového rámce každých 16,67 ms v tomto pořadí: 0, 1, 2, 0, 1, 2, 0, 1, 2. Umístění paměti DDR pro každý snímek se u obou VDMA liší, protože již nejsou navzájem synchronizovány. Místo toho se k synchronizaci pohybu dat mezi dvěma paměťovými místy používá hardwarový časovač (TTC1), nakonfigurovaný na 60 Hz.

Obrázek výše ukazuje 3 snímky, jejich rozměry a množství paměti, které každý vyžaduje (napravo od rámečku). Pokud těmto paměťovým místům přiřadíme zapisovací VDMA, pak můžeme načtená paměťová VDMA umístění přiřadit mimo tuto sadu, řekněme počínaje 0x0B000000. Každý snímek je tvořen 1280*720 pixely a každý pixel je tvořen 8 bity červené, zelené a modré barvy, celkem tedy 24 bitů. To znamená, že snímek je tvořen 1280*720*3 bajty (2,76 MB).

Uvnitř časovače IRQ, který je popsán v nastavení ovladače VDMA, bude zpracovávat kopírování dat mezi dvěma místy paměti VMDA. VDMA poskytuje ukazatel na aktuální rámec, do kterého se zapisuje nebo ze kterého se čte. Rámeček je reprezentován konkrétním šedým kódem, který je převeden v softwaru. Definice šedého kódu pro konfiguraci vyrovnávací paměti se 3 snímky lze nalézt v Průvodci produktem AXI VDMA v příloze C.

To nám umožňuje zkopírovat obsah zapsaný do paměti bez čtení z aktuálně zapisovaného rámce.

*** Pamatujte, že načtený VDMA se nepoužívá při odesílání dat přes bezdrátovou síť. Jejím jediným účelem je ověřit správnou funkci kopírování paměti ze zápisu VMDA. Čtení VMDA by mělo být zakázáno. ***

Zde jsou kroky k vytvoření bloku návrhu vysílače:

- Při vytváření nového projektu je dobré přiřadit k projektu čip nebo desku. Tento odkaz popisuje, jak přidat nové soubory desek do adresáře Vivado a přiřadit správnou desku k vašemu projektu. Bude se hodit při přidávání bloku Processing System a přechodu z hardwaru na software (strana SDK).

-

Přidejte následující bloky:

- dvi2rgb

- Video ve streamu Axi4

- Časový ovladač

- Axi4-stream k zobrazení

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Průvodce hodinami

- Konstantní

- Systém zpracování Zynq

- Při přidávání systému zpracování klikněte na „Spustit automatizaci bloků“na horním zeleném barevném pruhu a ujistěte se, že je vybrána možnost „Použít předvolbu desky“. Nechte vše ostatní výchozí.

- Obrázky každého okna konfigurace bloku najdete na obrázcích výše. Pokud pro konkrétní okno nevidíte obrázek, ponechte jej jako výchozí.

-

Začněte s konfigurací systému Zynq Processing:

- V konfiguraci PS-PL AXI Non Secure Enable GP Master AXI, enable M AXI GP0 Interface

- V konfiguraci PS-PL rozhraní HP Slave AXI povolte HP0 i HP1

- V konfiguraci MIO Ujistěte se, že je v části I/O periferie povolena ENET0, poté jednotka aplikačního procesoru, povolit časovač0

- V hodinové konfiguraci PL Fabric Clocks povolte FCLK_CLK0 a nastavte na 100 MHz.

- Klikněte na Ok

- Před kliknutím na „Spustit automatizaci připojení“nezapomeňte připojit video bloky, jak je vidět na obrázku návrhu bloku TX výše. Budete chtít přejmenovat konstantu na VDD a nastavit hodnotu na 1. Podle toho připojte video bloky.

- Udělejte hodiny a datové piny HDMI TMDS externí na blocích rgb2dvi a dvi2rgb

- Vytvořte vstupní a výstupní port pro signál detekce za provozu (HPD) a spojte je dohromady, tyto jsou definovány v souboru omezení

-

Hodiny pixelů jsou obnoveny z TMDS_Clk_p, který je vytvořen v souboru omezení. To bude 74,25 MHz v souladu s rozlišením 720p. Je důležité připojit pixelové hodiny (z bloku dvi2rgb) k následujícím pinům:

- vid_io_in_clk (vid in to axi stream block)

- vid_io_out_clk (stream axi do bloku vid out)

- clk (Timing Controller)

- PixelClk (rgb2dvi)

- *** Poznámka: Aby bylo možné aktivovat obnovu hodin pixelů, musí být konektory HDMI rx a tx zapojeny do aktivního zdroje/jímky. Jedním ze způsobů, jak to obejít, je oddělit bloky video rx a tx do různých hodinových domén (jinými slovy, vygenerovat nové hodiny 74,25 MHz, které budou napájeny do bloku tx). ***

- Dále nastavte průvodce hodinami tak, abyste měli vstup 100 MHz (globální zdroj vyrovnávací paměti) a 3 výstupní hodiny @ 50 MHz (hodiny AXI-Lite), 150 MHz (hodiny AXI4-Stream), 200 MHz (pin RefClk dvi2rgb).

- Připojte pin systému zpracování FCLK_CLK0 ke vstupu průvodce hodinami

- V tomto okamžiku klikněte na „Spustit automatizaci připojení“ze zeleného pruhu v horní části okna návrhu. Je dobré to udělat po jednom bloku a postupovat podle obrázku návrhu bloku TX výše.

- Nástroj se pokusí přidat propojení AXI, které funguje jako hlavní/podřízené propojení pro bloky, které používají sběrnici AXI-Lite (VDMA a GPIO).

- Přidá také AXI SmartConnect, který funguje jako propojení master/slave pro rozhraní AXI4-Stream a High Performance procesorů používaných VDMA (Stream to Memory Map a naopak).

- Nástroj také přidá Reset systému procesoru. Ujistěte se, že je připojen pouze k VDMA, GPIO a blokům souvisejícím s procesorem. Nepřipojujte jej k žádným blokům videa (tj. Dvi2rgb, řadič časování, video stream atd.)

- Jakmile bude automatizace připojení dokončena, ověřte, zda se připojení shodují s obrazem návrhu bloku TX. Všimnete si dalšího bloku System ILA, který nebyl zmíněn. Toto je pouze pro ladění a prozatím není potřeba. Používá reset procesoru 150M, takže to také není potřeba. Kdekoli vidíte malé zelené „chyby“na autobusech, je to kvůli ILA a lze je ignorovat.

- Posledním krokem je kliknutí pravým tlačítkem myši na návrh bloku ve stromu zdrojů projektu a výběr „Vytvořit HDL Wrapper“. Pokud máte v plánu přidat logiku do obálky, bude přepsána pokaždé, když ji vyberete.

- Podrobnosti o straně SDK najdete v části Nastavení ovladače VDMA.

Hodiny a resetování

Zjistil jsem, že nejdůležitějším aspektem každého projektu programovatelné logiky je pečlivé zvážení domén hodin a resetovacích signálů. Pokud jsou správně nakonfigurovány, máte dobrou šanci na to, aby váš design fungoval.

Pixel hodiny a načasování uzamčeny

Aby bylo možné ověřit, že jsou určité signály aktivní, je vhodné tyto signály spojit s LED diodami (hodiny, resety, zámky atd.). Dva signály, které mi pomohly sledovat na desce vysílače, byly pixelové hodiny a signál „uzamčeno“na bloku výstupu AXI4-Stream do videa, který vám říká, že časování videa bylo synchronizováno s časovacím ovladačem a zdrojem videa data. Do obálky návrhového bloku, která sleduje hodiny pixelů pomocí signálu PixelClkLocked na bloku dvi2rgb jako reset, jsem přidal nějakou logiku. Zde jsem připojil soubor jako hdmi_wrapper.v. Zde je také připojen soubor omezení.

Krok 2: Konfigurace programovatelné logiky Zynq pro přijímač

Programovatelný logický blok pro přijímač je jednodušší. Klíčovým rozdílem kromě chybějících vstupních bloků hdmi je absence obnovených hodin pixelů. Z tohoto důvodu musíme vygenerovat vlastní z průvodce hodinami. Tento návrh by měl být proveden v odděleném projektu od vysílače. Pro naše účely projekt přijímače sledoval desku Zybo 7Z-20, zatímco vysílač sledoval desku Z7-10. FPGA na deskách se liší, takže … buďte opatrní.

Zde jsou kroky k vytvoření bloku návrhu přijímače:

-

Přidejte do svého návrhu následující bloky IP:

- Časovač

- Výstup AXI4-Stream na video

- RGB na DVI

- AXI VDMA

- AXI GPIO

- Systém zpracování

- Průvodce hodinami

- Konstantní (VDD nastaveno na 1)

- Při konfiguraci těchto bloků postupujte stejně jako u vysílače. Zde byly zahrnuty obrázky pro pozoruhodné rozdíly v konfiguraci. Ostatní zůstávají stejné jako vysílač.

- Konfigurujte VDMA pro tento design pouze jako kanál pro čtení. Zakažte zapisovací kanál.

-

Průvodce hodinami by měl být nakonfigurován pro následující výstupy:

- clk_out1: 75 MHz (taktování pixelů)

- clk_out2: 150 MHz (hodiny proudu)

- clk_out3: 50 MHz (hodiny axi-lite)

- Připojte videobloky podle obrázku návrhu bloku RX.

- Poté spusťte automatizaci připojení, která přidá bloky AXI Interconnect, AXI SmartConnect a System Reset a pokusí se vytvořit příslušná připojení. Jděte pomalu sem, abyste se ujistili, že neprovádí nechtěná připojení.

- V bloku rgb2dvi vytvořte externí hodiny a datové piny HDMI TMDS

- U tohoto provedení není potřeba signál za provozu.

Krok 3: Nastavení ovladače VDMA

Nastavení pro různé bloky, které jsou konfigurovány prostřednictvím rozhraní AXI-Lite, se nejlépe provádí pomocí demo projektů zahrnutých v BSP jako reference. Po exportu návrhového hardwaru a spuštění sady SDK z Vivado budete chtít přidat nový balíček podpory desek a zahrnout knihovnu lwip202 do okna nastavení BSP. Otevřete soubor souboru system.mss z BSP a uvidíte ovladače periferií z vašeho návrhu bloku. Možnost „Příklady importu“vám umožňuje importovat demo projekty využívající tato periferie, a tak vám ukáže, jak je konfigurovat v softwaru pomocí dostupných ovladačů Xilinx (viz přiložený obrázek).

To byla metoda používaná pro konfiguraci VDMA, Timer & Interrupt a GPIO. Zde byl zahrnut zdrojový kód pro vysílání i příjem. Rozdíly jsou téměř výhradně v main.c.

*** POZNÁMKA: Jelikož systém v době psaní tohoto tutoriálu není plně funkční, zdrojový kód v této části neobsahuje kód bezdrátové sítě. V důsledku kombinace projektů přenosu/příjmu video jádra s projekty přenosu/příjmu v síti je třeba vyřešit několik chyb. Tento tutoriál s nimi prozatím zachází samostatně. ***

Funkce obsluhy přerušení TX (IRQHandler)

Tato funkce čte šedé kódy poskytované VDMA pro čtení i zápis prostřednictvím bloků GPIO. Šedé kódy jsou převedeny na desetinné číslo a použity pro výběr umístění základní paměti rámce aktuálního rámce. Zkopírovaný rámec je předchozím rámcem do rámce, na který je zapsán VDMA (např. Pokud VDMA zapisuje do rámce 2, zkopírujeme rámeček 1; pokud zapisujeme do rámce 0, zabalíme a čteme z rámce 2).

Tato funkce zachycuje pouze každý 6. snímek, aby se snížila snímková frekvence na 10 Hz, nikoli na 60 Hz. Horní hranice sítě je 300 Mb / s. Při rychlosti 10 snímků za sekundu je vyžadována šířka pásma 221,2 Mb / s.

Komentování/zrušení komentování dvou řádků v této funkci umožní uživateli přejít do režimu passthru HDMI pro účely ladění/testování (kód je označen pro označení příslušných řádků). Aktuálně kopíruje snímek do paměťového umístění používaného ethernetovým kódem.

Funkce obsluhy přerušení RX (IRQHandler)

Tato funkce je velmi podobná funkci TX, ale kopíruje se ze 2 vyrovnávací paměti FIFO, kterou ethernet používá k zápisu příchozích dat. Ethernetový kód označuje, do kterého rámce se zapisuje FIFO, data se kopírují z opačného rámce. Data se zkopírují do rámečku přímo za ten, který čte VDMA, aby nedošlo k roztržení.

Krok 4: Nastavení sítě Nanorouter

Chcete -li vytvořit síť pomocí nanorouterů TPlink, zapněte je jednotlivě a připojte se k výchozímu wifi SSID pro zařízení. Další informace o nastavení konfigurace pro toto konkrétní zařízení najdete v uživatelské příručce k zařízení.

Nastavte jedno ze zařízení jako přístupový bod, bude fungovat jako primární připojení k síti. Nezapomeňte pojmenovat síť a poznamenat si název a deaktivovat DHCP (nechceme, aby router dynamicky konfiguroval IP adresy, chceme, aby desky tansmitter a přijímač Zybo samy nastavovaly své IP adresy, aby byly konzistentní). Po konfiguraci se ujistěte, že se zařízení restartuje a vytvoří tuto síť.

Nastavte druhé zařízení jako klienta a ujistěte se, že se připojuje k síťovému SSID, který jste nastavili pomocí prvního nanorouteru. Ještě jednou se ujistěte, že je DHCP pro klienta zakázáno.

Jakmile klient dokončí a restartuje počítač, měl by se připojit k nanorouteru přístupového bodu (pokud tomu tak není, je pravděpodobně problém ve vaší konfiguraci jednoho ze zařízení). Jakmile se připojí k přístupovému bodu, všimnete si, že LED dioda na klientovi bude svítit.

V tomto bodě bude nanorouter LED přístupového bodu pravděpodobně nadále blikat, to je v pořádku! Blikající světlo znamená, že není připojeno k jinému zařízení z ethernetového portu, a jakmile je připojeno ke konfigurovanému Zybo, LED dioda zůstane svítit, což indikuje úspěšné připojení k síti.

Nyní, když máme nastavení našich nanorouterů, máme bezdrátovou síť, která nám umožní komunikovat prostřednictvím. Důležitou poznámkou je, že naše konfigurační metoda pro nanoroutery (jako přístupový bod a klient) nám umožňuje komunikovat z vysílací desky Zybo na přijímající desku Zybo, jako by byly tyto dva propojeny jediným ethernetovým vodičem. Díky tomu je nastavení naší sítě méně obtížné, protože alternativa by pravděpodobně zahrnovala konfiguraci desek Zybo pro výslovné připojení k serveru spolu s zamýšleným připojením.

Jakmile jsou obě zařízení nastavena, jsou nanoroutery nakonfigurovány a připraveny k implementaci do vaší sítě WIDI. Neexistuje žádné specifické párování mezi nanoroutery a deskami Zybo, protože přístupový bod nebo klient bude fungovat buď pro vysílací nebo přijímací zařízení.

Krok 5: Nastavení systému zpracování Zynq pro přenos dat přes ethernet

Abychom mohli přenášet data HDMI z jedné desky Zybo na druhou, musíme do našeho ovladače VDMA začlenit ethernetový protokol. Našim cílem je streamovat jednotlivé video snímky přes ethernetové periferie v systému zpracování, a to nastavenou rychlostí, která je v souladu s šířkou pásma naší sítě. Pro náš projekt jsme použili TCP poskytovaný API Bw-metal LwIP API. Vzhledem k tomu, že oba členové projektu mají relativně málo zkušeností se síťovými nástroji, byla tato volba provedena bez plného uznání důsledků a omezení spojených s TCP. Hlavním problémem této implementace byla omezená šířka pásma a skutečnost, že opravdu není navržena pro účely páření velkých objemů dat. Alternativní řešení pro nahrazení TCP a vylepšení tbe v tomto projektu budou probrána později.

Stručný popis TCP s LwIP: Data jsou odesílána po síti v paketech velikosti tcp_mss (maximální velikost segmentu TCP), která je obecně 1460 bajtů. Volání tcp_write bude vyžadovat některá data odkazovaná ukazatelem a nakonfigurovat pbufs (vyrovnávací paměti paketů) pro uložení dat a poskytnutí struktury pro operace TCP. Maximální množství dat, které lze najednou zařadit do fronty, je nastaveno jako tcp_snd_buf (vyrovnávací paměť odesílatele TCP). Protože tento parametr je 16bitové číslo, jsme omezeni na velikost vyrovnávací paměti pro odesílání 59695 bajtů (ve vyrovnávací paměti pro odesílání je určité požadované odsazení). Jakmile jsou data zařazena do fronty, zavolá se tcp_output pro zahájení přenosu dat. Před odesláním dalšího segmentu dat je nutné, aby byly úspěšně přeneseny všechny předchozí pakety. Tento proces se provádí pomocí funkce recv_callback, protože se jedná o funkci, která se volá, když je z přijímače vidět potvrzení.

Využití ukázkových projektů v sadě Vivado SDK je velmi užitečné pro naučení se provozu LwIP TCP a je dobrým výchozím bodem pro zahájení nového projektu.

Postup pro vysílací zařízení WiDi je následující:

- Inicializujte síť TCP pomocí volání funkce ovladače LWIP s holým kovem.

- Zadejte všechny funkce zpětného volání nezbytné pro síťové operace.

- Připojte se k přijímači WiDi připojením k jeho IP adrese a portu (naše konfigurace: IP přijímače je 192.168.0.9, připojení k portu 7).

- Po vypršení časovače ovladače VDMA zadejte TX ISR.

- Určete aktuální vyrovnávací paměť rámců pro přístup na základě šedého kódu VDMA

- Zařaďte do fronty první segment dat ve vyrovnávací paměti pro odesílání TCP

- Vytvořte výstup dat a aktualizujte místní proměnné, abyste měli přehled o tom, kolik dat bylo odesláno z aktuálního rámce.

- Po dosažení přijatého zpětného volání (volání funkce provedené poté, co vysílač obdrží potvrzení o načtení dat), zařaďte do fronty další segment dat.

- Kroky 7 a 8 opakujte, dokud nebude odeslán celý snímek.

- Vraťte se do klidového stavu a počkejte na další přerušení časovače, abyste označili, že je nový snímek připraven (Zpět na krok 4).

Ujistěte se, že jste nastavili nastavení LwIP balíčku podpory desky, jak je znázorněno na obrázku výše. Všechny hodnoty jsou výchozí kromě tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Všimněte si také, že podrobného ladění lze dosáhnout změnou parametrů BSP pro skupinu debug_options.

Krok 6: Nastavení systému zpracování Zynq pro příjem dat přes ethernet

Vývojová deska Zybo, která bude fungovat jako bezdrátový přijímač, bude fungovat podobně jako vysílací zařízení. Nastavení balíčku podpory desky pro LwIP bude totožné s nastavením v předchozím kroku.

Zařízení přijme pakety obsahující segmenty video rámců z nanorouteru a zkopíruje data rámce videa do vyrovnávací paměti trojitého rámce pro přijímající VDMA. Aby nedocházelo k přepisování jakýchkoli dat, používá se při shromažďování dat z nanorouteru dvojitá vyrovnávací paměť dat (budeme ji označovat jako síťová vyrovnávací paměť), takže síťový provoz může pokračovat ve streamování, zatímco se předchozí plný rámec videa kopíruje do Vyrovnávací paměť VDMA.

Postup pro přijímací zařízení WiDi vyžaduje dva úkoly, z nichž jeden přijímá ethernetová data a druhý kopíruje video snímky ze síťové vyrovnávací paměti do vyrovnávací paměti trojitých snímků VDMA.

Úkol příjmu ethernetu:

- Inicializujte síť TCP pomocí volání funkce ovladače LWIP s holým kovem (nastavení s IP adresou, ke které se vysílač připojí, 192.168.0.9 v naší)

- Zadejte všechny funkce zpětného volání nezbytné pro síťové operace.

- Po obdržení ethernetového paketu zkopírujte data paketu do aktuální síťové vyrovnávací paměti, zvyšte aktuální nahromaděná data.

- Pokud paket vyplňuje vyrovnávací paměť rámce sítě, pokračujte kroky 5 a 6. V opačném případě přejděte zpět ke kroku 3 tohoto úkolu.

- signál, že úloha vyrovnávací paměti trojitého rámce VDMA by měla kopírovat z nově dokončené síťové vyrovnávací paměti.

- Přepněte na jinou síťovou vyrovnávací paměť a pokračujte ve shromažďování dat přes ethernet.

- Nečinný, dokud není přijat nový ethernetový paket (krok 3).

Zkopírujte síťovou vyrovnávací paměť do vyrovnávací paměti trojitého rámce VDMA:

- Po vypršení časovače ovladače VDMA zadejte RX ISR.

- Určete aktuální vyrovnávací paměť rámců pro přístup na základě šedého kódu VDMA.

- Určete, která síťová vyrovnávací paměť bude zkopírována do vyrovnávací paměti VDMA, a zkopírujte tato data

Krok 7: Připojte desky Zybo ke zdroji HDMI a HDMI dřezu

Nyní připojte kabely HDMI pro přijímač i vysílač, naprogramujte FPGA a spusťte systém zpracování. Rychlost snímků bude pravděpodobně velmi pomalá, kvůli obrovské režii v provozu LwIP a omezené šířce pásma. Pokud jsou nějaké problémy, připojte se přes UART a zkuste identifikovat všechna varování nebo chyby.

Krok 8: Alternativní nápady na vylepšení

Velkým problémem tohoto projektu bylo množství dat potřebných k odeslání přes wifi. To se očekávalo, nicméně jsme podcenili dopad, který by to mělo, a vedlo to spíše k výbuchu obrázků na obrazovce než k vysílání videa. Existuje několik způsobů, jak tento projekt zlepšit:

- Komprese videa v reálném čase. Komprimace příchozího videa mezi snímky by výrazně snížila množství dat potřebných k odeslání po síti. V ideálním případě by to bylo provedeno v hardwaru (což není snadný úkol), nebo by to mohlo být provedeno v softwaru pomocí druhého jádra ARM ke spuštění kompresních algoritmů (to by vyžadovalo nějakou další analýzu, aby se zajistilo, že načasování vyjde). Na webu jsme našli některé komponenty pro kompresi videa v reálném čase s otevřeným zdrojovým kódem, ale většina z nich je IP.

- Implementace ethernetového proudu v hardwaru, nikoli v softwaru. Kvůli nedostatku místa, které je k dispozici pro frontu odchozích dat ve vysílači, kvůli omezení velikosti segmentu, byla spousta režie. Mnohem efektivnější proces je použít AXI Ethernet IP s vyrovnávací pamětí FIFO nebo DMA k přenosu dat do něj. To by snížilo další zavazadlo z LwIP TCP a umožnilo by více toku dat.

Krok 9: Usnadnění

Výsledným produktem tohoto projektu WiDi by měla být plně integrovaná, kompaktní dvojice zařízení, která by uživatel mohl připojit k jakémukoli zdroji HDMI a poté potopit přenos videa na displej s možností HDMI bezdrátově. Zařízení by měla obsahovat SoC Zynq-7000, který se nachází na referenční desce Zybo, a začlenit síťový hardware nalezený v nano-routerech TP-Link. V ideálním případě by uživatel mohl ovládat vysílací modul z diskrétního umístění v cílovém operačním systému s malou potřebou významné technické schopnosti.

Zabezpečení a konektivita

Zařízení by měla také obsahovat zabezpečení TLS (Transport Layer Security) a omezené možnosti automatického připojení, a to z důvodu ochrany osobních údajů. Záměrem designérů je, aby spojení s displejem přes bezdrátové rozhraní bylo záměrnou akcí jménem uživatele, aby se předešlo omylu v přenosu citlivého materiálu.

Současný stav

Do tohoto bodu je stav projektu stále velmi nedokončený. Aby mohl aktuální uživatel koncového bodu těžit z tohoto kurzu, musí mít silné technické znalosti o návrhu vestavěného systému a měl by mít určitou znalost spolupráce programovatelného hardwaru a vestavěného softwaru.

Data odesílaná po síti nejsou v tomto okamžiku šifrována a předpokládá se, že jde o hrubý přenos paketů TCP/IP.

Projekt jádra videa byl úspěšně testován pro vysílání i příjem. Na druhé straně bylo navázáno bezdrátové spojení mezi dvěma deskami zybo a data testovacího rámce byla úspěšně odeslána. Stále je však nutné kombinovat síťový kód s každým projektem jádra videa a testovat přenos skutečných rámců videa.

Doporučuje:

DIY ESP32 Development Board - ESPer: 5 kroků (s obrázky)

DIY ESP32 Development Board - ESPer: Takže nedávno jsem četl o spoustě IoT (Internet of Things) a věřte mi, prostě jsem se nemohl dočkat, až otestuji jedno z těchto nádherných zařízení, s možností připojení k internetu, sám a dostávám ruce do práce. Naštěstí příležitost

Přepínání světel ovládané pomocí mrknutí očí pomocí brýlí na hlavu Shota Aizawa (My Hero Academia): 8 kroků (s obrázky)

Přepínání světel ovládané pomocí Eye-Blink pomocí gumových hlavic Shota Aizawa (My Hero Academia): Pokud čtete manga mé hrdiny akademie nebo sledujete anime mého hrdiny, musíte znát postavu jménem shota aizawa. Shota Aizawa, také známá jako Eraser Head, je profesionální hrdina a učitelka homeroom třídy U-Class 1-A. Shota's Quirk mu dává ab

JALPIC One Development Board: 5 kroků (s obrázky)

JALPIC One Development Board: Pokud sledujete mé projekty Instructables, víte, že jsem velkým fanouškem programovacího jazyka JAL v kombinaci s mikrokontrolérem PIC. JAL je programovací jazyk podobný Pascalu vyvinutý pro 8bitové mikrokontroléry PIC společnosti Microchip. Mo

Zpracování videa pomocí VHDL a Zybo: 10 kroků

Zpracování videa pomocí VHDL a Zybo: FPGA zpracovává rychleji než CPU, protože může provádět mnoho výpočtů souběžně Poznámka: Tento projekt je stále ve výstavbě a bude vylepšen (jakmile budu mít čas). Mezitím cestuji po světě

Kvadrokoptéra využívající desku Zybo Zynq-7000: 5 kroků

Kvadrokoptéra využívající desku Zybo Zynq-7000: Než začneme, zde jsou některé věci, které byste chtěli k projektu: Seznam dílů 14 Střídavých motorů 1100KV 4x