Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:24.

- Naposledy změněno 2025-01-23 14:38.

Toto je návod, jak vytvořit minutové stopky pomocí VHDL a desky Basys 3. Takové zařízení je ideální pro hry, kde každý hráč má maximálně jednu minutu na svůj tah. Stopky na sedmisegmentovém displeji přesně zobrazují sekundy a milisekundy, počínaje 0 sekundami a 0 milisekundami, až 60 sekund a 0 milisekund. Používají se také dvě tlačítka: střední tlačítko sloužící ke spuštění, zastavení a pokračování časovače a pravé tlačítko slouží k restartování časovače. Když je zařízení porovnáno bok po boku s vestavěnými stopkami chytrého telefonu, je přesnost hodin znatelná.

Krok 1: Získejte hardware/software

1. Basys 3 Artix-7 FPGA Trainer Board od společnosti Digilent s kabelem Micro-USB na USB

2. Vivado 2016.2 Design Suite od Xilinx

Krok 2: Blokový diagram

Tento obvod je konstruován behaviorálně a používá vestavěné komponenty Xilinx, ale může být také popsán strukturálně, jak ukazuje obecný strukturální diagram výše. Z diagramu je vidět, že obvod je poháněn dvěma frekvenčními děliči. Jeden z frekvenčních děličů běží 1 centisekundu a pohání katodový čítač, který se používá jako čísla zobrazená na sedmisegmentovém displeji. Druhý dělič kmitočtů běží na 240 Hz a slouží k pohonu čítače anod, který se otáčí anodami, takže se všechna čísla na sedmisegmentovém displeji zobrazují správně. Kodér odebírá katodovou logiku z katodového čítače a anodovou logiku z anodového čítače a kóduje ji na výstupní katodu a anodu, která spouští sedmisegmentový displej. Funkce tohoto kodéru je, aby se výstup katody měnil pokaždé, když se změní výstup anody. Katodový výstup nelze spustit nezávisle na čítači, protože anody se musí otáčet přes 4 samostatné číslice.

Krok 3: Modul projektu

Za prvé, procesní blok pro CEN je vytvořen tak, že když je detekováno stisknutí tlačítka, ENABLE se přepne. Toto slouží jako zastavení/spuštění katodového čítače.

V dalším procesním bloku jsou hodinové signály centisekund a 240 Hz nastaveny tak, aby se jejich příslušné čítače zvýšily o 1 pokaždé, když vnitřní hodiny 100 MHz dosáhnou stoupající hrany. Jakmile čítač centisekund dosáhne 500 000, resetuje se zpět na 0. Mezitím se čítač 240 Hz resetuje, jakmile počet dosáhne 41667.

Pokud je pro část katody kódu, pokud je ENABLE '0', počítání katody se pozastaví. Pokud během této doby stisknete resetovací tlačítko, všechny počty se resetují na „0000“. Mezitím, pokud je ENABLE '1', počítání katody bude pokračovat, dokud počet katod nedosáhne 60,00, ve kterém spustí stop signál na '1'. Signál zastavení směřuje zpět do procesního bloku CEN a způsobí, že ENABLE bude '0', zatímco signál zastavení je '1', a nezmění se, dokud nestisknete tlačítko reset.

Nakonec je sedmisegmentový displej nastaven tak, že 4 anody jsou správně spojeny s každou z jejich 8 katod, aby se současně zobrazily jejich příslušné číslice 0-9.

Krok 4: Omezení

Tento soubor omezení spojuje určené vstupy a výstupy z VHDL do nezbytných fyzických částí desky Basys. Pro tento projekt komponenty obsahují čtyři anody a každou z jejich osmi katod pro sedmisegmentový displej, interní hodiny 100 MHz, středové tlačítko a pravé tlačítko.

Krok 5: Test

Jakmile kód dokončíte, můžete nyní programovat FPGA pomocí kabelu USB. Sedmisegmentový displej by měl ukazovat 0,00. Otestujte, zda tlačítka fungují, stisknutím středového tlačítka spusťte časovač, dokud nedosáhne 60,00 hodin a nezastaví se; kdykoli mezi tím můžete pozastavení pozastavit opětovným stisknutím středového tlačítka. Jakmile je pozastaveno, můžete stisknutím pravého tlačítka resetovat časovač zpět na 0,00. Pokud vše funguje správně, gratulujeme, že jste právě vytvořili minutový časovač!

Doporučuje:

Udržování stopky jednoduché internetové rádio: KISSIR: 13 kroků

Udržování stopky jednoduché internetové rádio: KISSIR: Někdy to prostě musí být hmatové. Žádné rozhraní jakéhokoli druhu. Jen tlačítka. Raspberry Pi jako přehrávač internetového rádia není nic nového a existuje spousta návodů, jak vytvořit přehrávač internetového rádia pomocí malinového pi s nebo bez

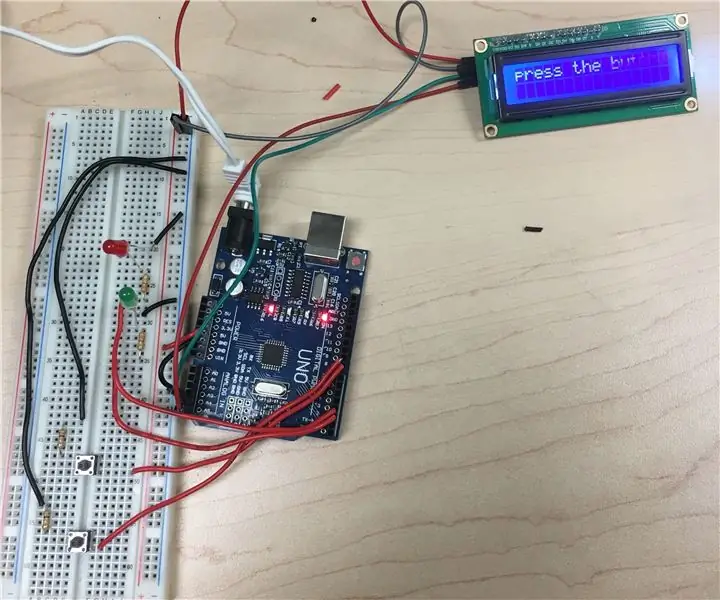

Stopky Arduino pomocí I2C LCD: 5 kroků

Stopky Arduino pomocí I2C LCD: V tomto projektu vás naučím používat LCD displej a Arduino jako interaktivní stopky. Když je váš projekt hotový s poskytnutým kódem, měl by vypadat jako na fotografii výše. Přejděte na další krok a zjistěte, kde začít

Automatické stopky: 9 kroků

Automatické stopky: Tento návod vám ukáže, jak vytvořit automatické stopky. Protože běh je zábava, ale někdy s sebou nemáte nikoho, kdo by vás dokázal načasovat. Snažil jsem se, aby to bylo co nejjednodušší, nejlevnější a nejpřesnější. Nepotřebujete dálkové ovládání

Základní stopky pomocí desky VHDL a Basys3: 9 kroků

Základní stopky pomocí desky VHDL a Basys3: Vítejte v instruktáži, jak vytvořit stopky pomocí základní desky VHDL a Basys 3. Jsme nadšeni, že s vámi můžeme sdílet náš projekt! Toto byl závěrečný projekt pro kurz CPE 133 (Digital Design) na Cal Poly, SLO na podzim 2016. Projekt, který jsme postavili

Stopky VHDL: 8 kroků (s obrázky)

VHDL stopky: Toto je návod, jak vytvořit stopky pomocí VHDL a desky s obvody FPGA, jako je deska Basys3 Atrix-7. Stopky dokážou počítat od 00,00 s do 99,99 s. Používá dvě tlačítka, jedno pro tlačítko start/stop a druhé pro