Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:22.

- Naposledy změněno 2025-01-23 14:38.

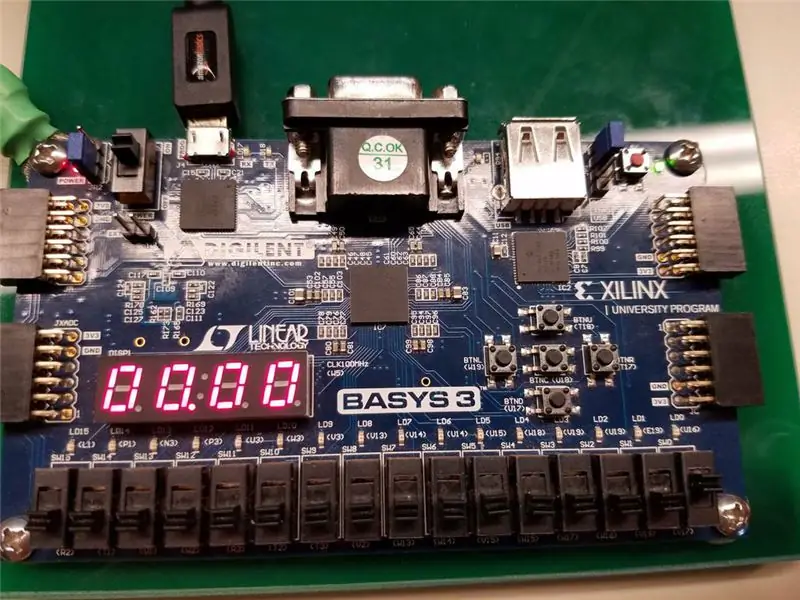

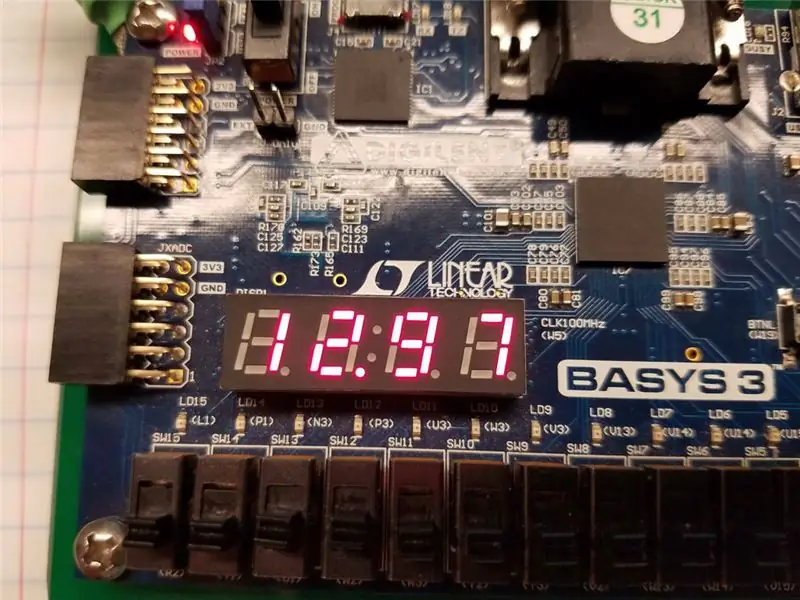

Vítejte v instruktáži, jak vytvořit stopky pomocí základní desky VHDL a Basys 3. Jsme nadšeni, že s vámi můžeme sdílet náš projekt! Toto byl závěrečný projekt pro kurz CPE 133 (Digital Design) na Cal Poly, SLO na podzim 2016. Projekt, který jsme vytvořili, jsou jednoduché stopky, které začínají, resetují a pozastavují čas. Jako vstupy jsou zapotřebí tři tlačítka na desce Basys3 a čas se zobrazuje na čtyřmístném sedmisegmentovém displeji desky. Uplynulý čas se zobrazuje ve formátu sekund: centisekund. Jako vstup ke sledování uplynulého času používá systémové hodiny desky a vydává čas do čtyř číslic sedmisegmentového displeje.

Krok 1: Materiály

Materiály, které budete pro tento projekt potřebovat:

- 1 počítač s Vivado Design Suite WebPack nainstalovaným od Xilinx (preferujte verzi 2016.2)

- 1 deska Digilent Basys3 Xilinx Artix-7 FPGA

- 1 kabel portu USB

Krok 2: Nastavení vstupů a výstupů

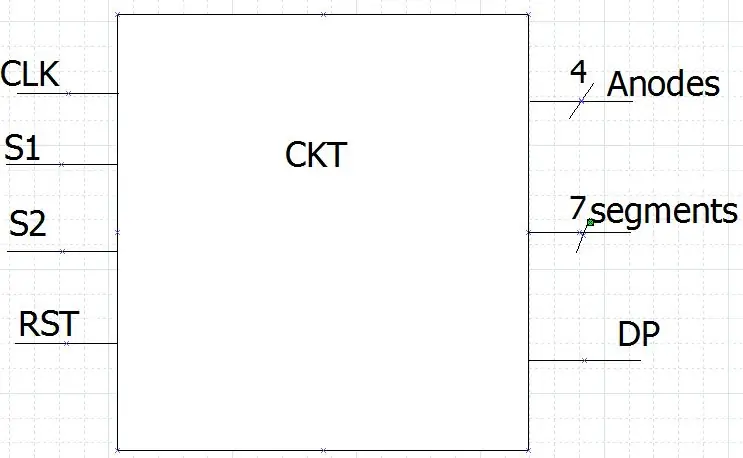

Na výše uvedeném obrázku je blokové schéma nejvyšší úrovně hlavního modulu stopek. Stopky přijímají vstupy „CLK“(hodiny), „S1“(tlačítko start), „S2“(tlačítko pozastavení) a „RST“(reset) a mají 4bitový výstup „Anodes“, 7bitový výstupní „segment“a jednobitový výstup „DP“(desetinná tečka). Když je vstup „S1“vysoký, stopky začnou počítat čas. Když je „S2“nízké, stopky pozastaví čas. Když je „RST“vysoké, stopky se zastaví a vynulují čas. V obvodu jsou čtyři submoduly: dělič hodin, čítač číslic, ovladač sedmisegmentového displeje a kodér sedmisegmentového displeje. Hlavní modul stopek spojuje všechny submoduly dohromady a se vstupy a výstupy.

Krok 3: Výroba hodin

Modul děliče hodin přebírá systémové hodiny a pomocí vstupu děliče vytváří hodiny jakékoli rychlosti, která není větší než rychlost systémových hodin. Stopky používají dva různé moduly hodin, jeden vytváří hodiny 500 Hz a druhý hodiny 100 Hz. Schéma děliče hodin je znázorněno na obrázku výše. Dělič hodin má jednobitový vstup „CLK“a 32bitový vstup „Divisor“a jednobitový výstup „CLKOUT“. „CLK“jsou systémové hodiny a „CLKOUT“jsou výsledné hodiny. Modul také obsahuje bránu NOT, která přepíná signál "CLKTOG", když počet dosáhne hodnoty děliče.

Krok 4: Počítání do deseti

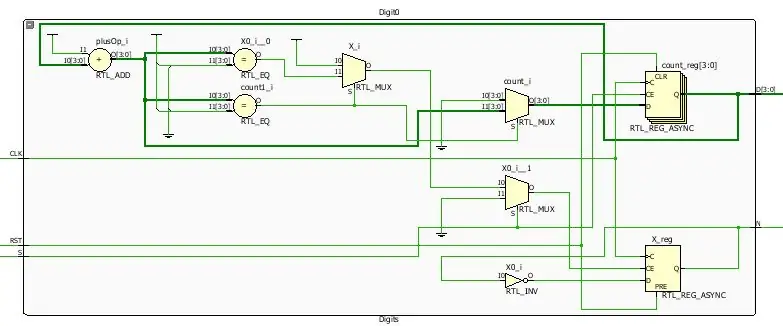

Čítač číslic počítá každou číslici od 0 do 10 a vytváří další hodiny, aby další číslice fungovala z toho, co osciluje, když počet dosáhne 10. Modul přijímá 3 jednobitové vstupy „S“, „RST“a „CLK“"a výsledkem je jednobitový výstup" N "a 4bitový výstup" D ". Vstup „S“je vstup povolení. Hodiny se zapnou, když je „S“vysoko, a vypnou se, když je „S“nízko. „RST“je resetovací vstup, takže se hodiny resetují, když je „RST“vysoké. „CLK“je hodinový vstup pro čítač číslic. "N" je hodinový výstup, který se stane vstupním taktem pro další číslici. Výstup „D“představuje binární hodnotu číslice, na které se čítač nachází.

Krok 5: Zobrazení čísel

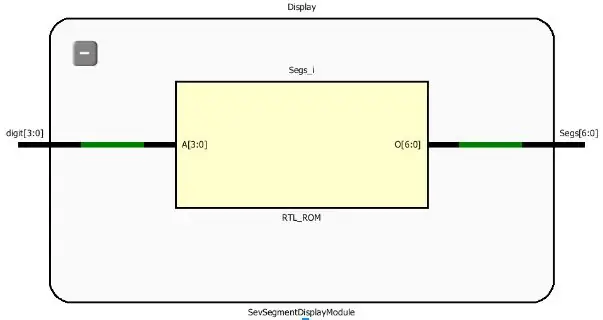

Sedmisegmentový kodér displeje zakóduje binární číslo přijaté z modulu ovladače sedmisegmentového displeje a přemění ho na proud bitů, které budou interpretovány jako hodnoty „1“nebo „0“pro každý segment displeje. Binární číslo je modulem přijímáno jako 4bitová vstupní „číslice“a výsledkem jsou 7bitové výstupní „segmenty“. Modul se skládá z jednoho bloku procesního případu, který přiřazuje konkrétní 7bitový proud pro každou možnou vstupní hodnotu od 0 do 9. Každý bit v sedmibitových proudech představuje jeden ze sedmi segmentů číslic na displeji. Pořadí segmentů ve streamu je „abcdefg“, přičemž „0“představuje segmenty, které se pro dané číslo rozsvítí.

Krok 6: Jak zobrazit stopky

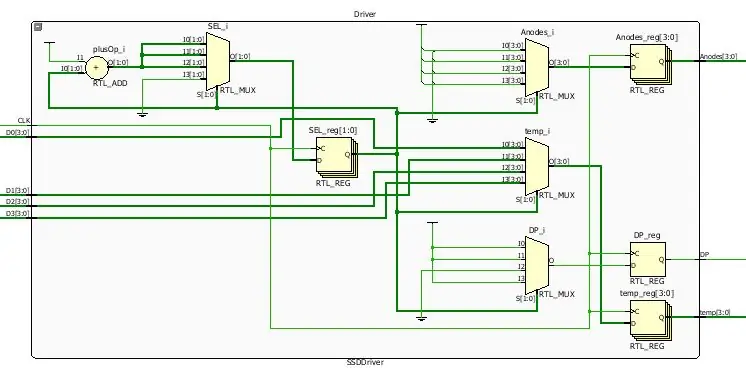

V modulu ovladače sedmisegmentového displeje jsou čtyři 4bitové vstupy „D0“, „D1“, „D2“a „D3“, přičemž každý představuje čtyři číslice, které se mají zobrazit. Vstup „CLK“je hodinový vstup systému. Jednobitový výstup „DP“představuje desetinnou čárku na sedmisegmentovém displeji. 4bitový výstupní „Anody“určuje, která číslice na sedmisegmentovém displeji se zobrazí, a 4bitový výstupní „temp“závisí na stavu 2bitového řídicího vstupu „SEL“. Modul používá 4 multiplexory pro řídicí vstup „SEL“a tři výstupy; „Anody“, „teplota“a „DP“.

Krok 7: Sloučení všeho dohromady

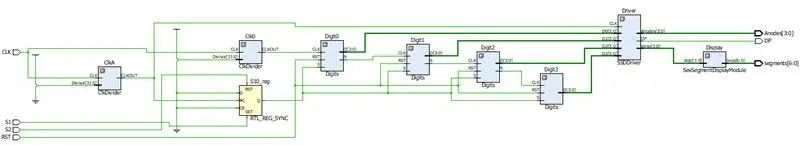

K vytvoření tlačítek start a pauza se používá procesní blok „pokud“běžící mimo hodiny 500 Hz. Poté propojte všechny submoduly dohromady v hlavním modulu stopek deklarováním komponent každého jednotlivého submodulu a použitím různých signálů. Číslicové submoduly přebírají hodinový výstup předchozího digitálního submodulu, přičemž první přijímá hodiny se 100 Hz. Výstupy „D“digitálních submodulů se poté stanou vstupy „D“modulu modulu sedmisegmentového displeje. A nakonec výstup „temp“modulu sedmisegmentového ovladače displeje se stane vstupem „temp“modulu sedmisegmentového kodéru.

Krok 8: Omezení

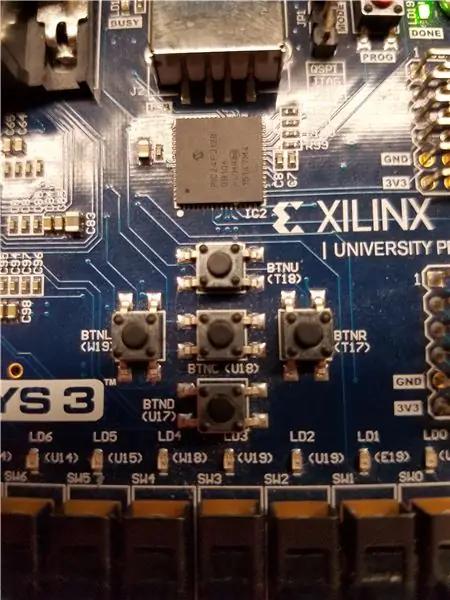

Pro vstupy „RST“, „S1“a „S2“použijte 3 tlačítka (W19, T17 a U18). W19 je resetovací tlačítko, T17 je startovací tlačítko (S1) a U18 je tlačítko pauzy (S2). Omezení pro vstup hodinového vstupu je také vyžadováno pomocí portu W5. Nezapomeňte také přidat tento řádek do omezení hodin:

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

Také propojte anody a segmenty s deskou, aby se stopky zobrazovaly na sedmisegmentovém displeji, jak je vidět v souboru omezení.

Krok 9: Testování

Zajistěte, aby vaše zařízení fungovalo, a to tak, že si zahrajete se třemi tlačítky: stisknete a podržíte je v každém možném pořadí, abyste našli případné problémy s vaším kódem.

Doporučuje:

Reproduktor základní desky PCB: 5 kroků (s obrázky)

Reproduktor základní desky s plošnými spoji: Nejčastěji vybíráme různé typy elektronických obvodů. Nula! Espero que gostem: DSe eu ganhar algum dos principais prêmios eu pretendo levar na Universidade e availableibilizar para os alunos e profesores využití de cutoç

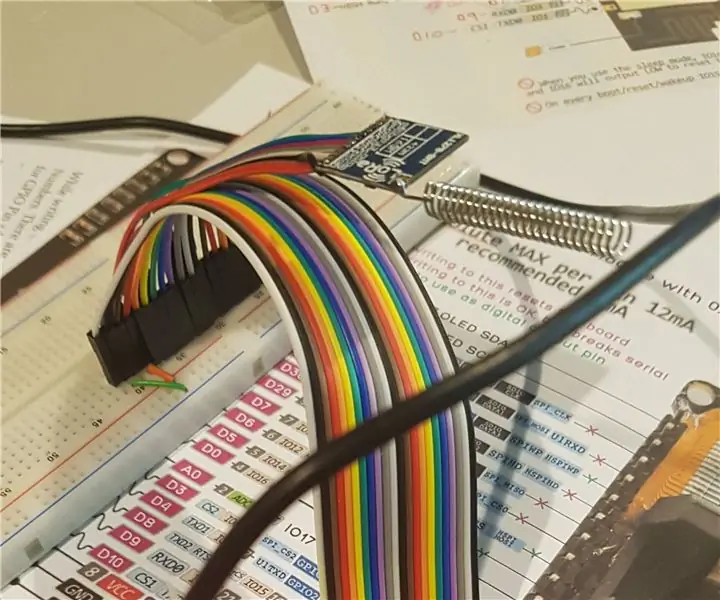

Získání práce s LoRa (SX1278/XL1278-SMT) přes SPI na modulu základní desky WeMos D1 ESP-12F ESP8277 s OLED: 7 kroků

Získání LoRa (SX1278/XL1278 -SMT) Práce přes SPI na modulu základní desky WeMos D1 ESP -12F ESP8277 s OLED: Vypracování mi trvalo týden - zdá se, že na to nikdo přede mnou nepřišel - tak doufám, že vás to zachrání nějaký čas! Nešikovně pojmenovaný modul základní desky „WeMos D1 ESP-12F ESP8266 s 0,96 palcovou obrazovkou OLED“je vývojová deska za 11 $

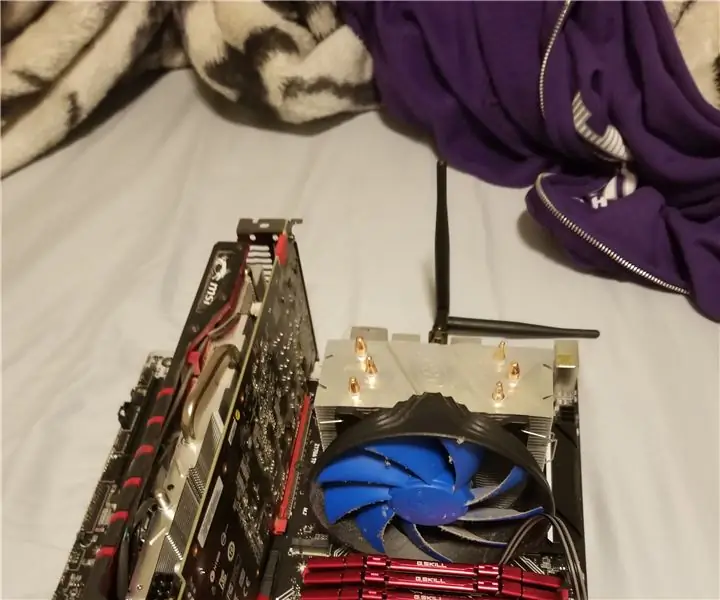

Sestavení základní desky (minus procesor): 10 kroků

Sestavení základní desky (minus procesor): S tímto návodem se naučíte sestavovat různé odnímatelné součásti. z důvodu nedostatečné dostupnosti tepelné pasty nedojde k sestavení procesoru

Jednominutové stopky VHDL: 5 kroků

VHDL One Minute stopwatch: This is a tutorial on how to build a one minute stopwatch using VHDL and a Basys 3 board. Takové zařízení je ideální pro hry, kde každý hráč má maximálně jednu minutu na svůj tah. Stopky přesně zobrazují sekundy a milisekundy

Výměna základní desky Dell 6850: 29 kroků

Vyměňte základní desku Dell 6850: Takto vyměníte základní desku Dell 6850. Pokud zjistíte, že máte náhradní základní desku a nemáte žádnou oficiální technologii, která by vám to mohla změnit, můžete to udělat sami, není to tak těžké, pokud víte o modrém tlačítku. Tohle jsou