Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:24.

- Naposledy změněno 2025-01-23 14:38.

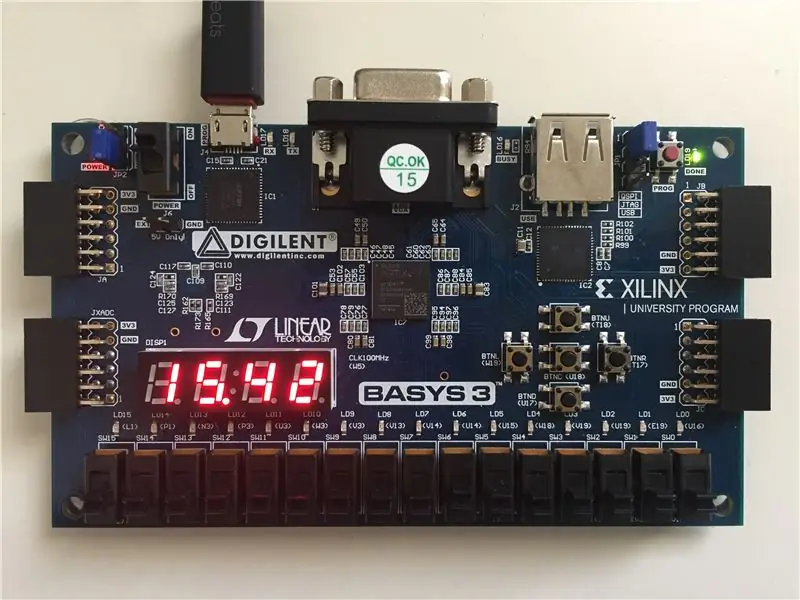

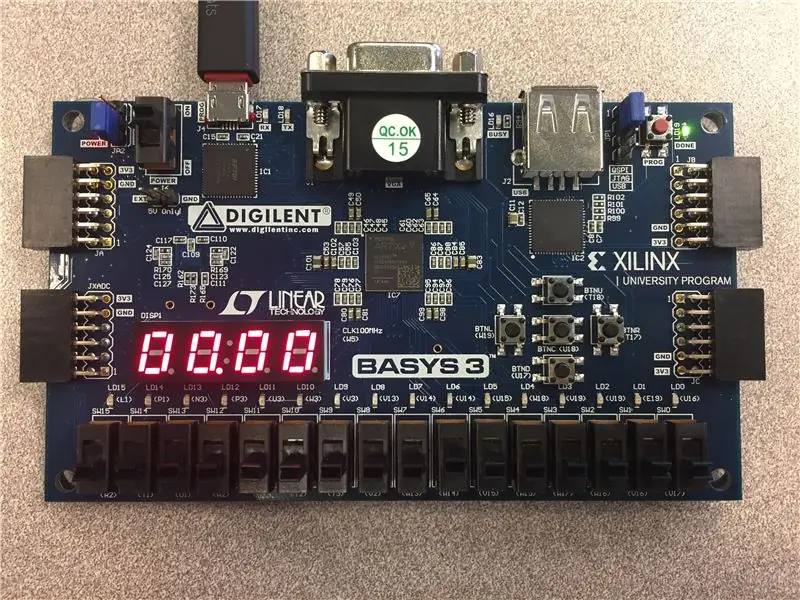

Toto je návod, jak vytvořit stopky pomocí VHDL a desky s obvody FPGA, jako je deska Basys3 Atrix-7. Stopky dokážou počítat od 00,00 s do 99,99 s. Používá dvě tlačítka, jedno pro tlačítko start/stop a druhé pro tlačítko reset. Čísla se zobrazují na sedmisegmentovém displeji desky pomocí jeho anod a katod. Aby tyto stopky fungovaly, jsou potřeba tři různé soubory.

Krok 1: Hardware/Software

- Deska FPGA Basys3 Atrix-7

- Vivado Design Suite od Xilinx

- USB 2.0 A samec na Micro-B samec

Krok 2: Blokový diagram

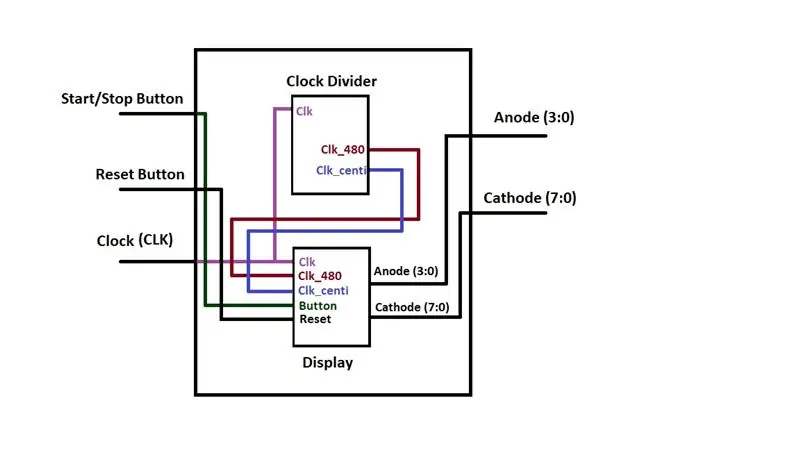

Celkové stopky mají tři vstupy a dva výstupy. Tři vstupy jsou start/stop, reset a hodiny. Start/stop a reset jsou tlačítka a hodiny jsou na desce s frekvencí 100 MHz. Dva výstupy jsou anody a katody pro sedmisegmentový displej.

První modul (dělič hodin) má jeden vstup a dva výstupy. Vstupem jsou hodiny na desce s frekvencí 100 MHz a výstupy jsou dva samostatné hodiny, jeden běží na 480 Hz a druhý běží na 0,5 MHz.

Druhý modul (displej) má pět vstupů a dva výstupy. Vstupy jsou hodiny 100 MHz na desce, dva hodiny z modulu děliče hodin a tlačítka start/stop a reset. Výstupy jsou anody a katody.

Poslední modul (modelovaný celým blokovým schématem) má tři vstupy a dva výstupy. Toto je soubor, který spojuje všechno dohromady. Vstupy jsou 100 MHz na desce a tlačítka start/stop a reset. Výstupy jsou anody a katody, které ovládají sedmisegmentový displej. Všechny vstupy a výstupy jsou fyzicky na desce pro finální modul.

Krok 3: Stavový diagram

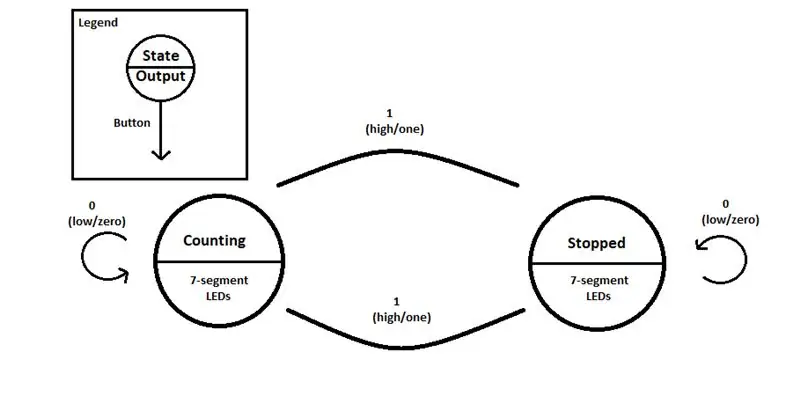

Obrázek výše ukazuje stavový diagram fungování stopky. Stisknutím resetovacího tlačítka není ovlivněn stav stopek. Další stav je určen tlačítkem start/stop. Start/stop je při stisknutí „VYSOKÝ“, ale ne při jeho podržení, a „NÍZKÝ“, když se tlačítko odrazilo zpět nebo bylo přidrženo poté, co bylo na okamžik „VYSOKÉ“.

Pokud stopky počítají a tlačítko start/stop přejde na „VYSOKÉ“, pak se počítání zastaví. Pokud se stopky zastaví a tlačítko start/stop přejde na „HIGH“, začne znovu počítat. Pokud je u obou stavů tlačítko start/stop „NÍZKÉ“, pak zůstane ve stavu, ve kterém se aktuálně nachází.

Krok 4: Modul děliče hodin

Modul děličů hodin má jeden vstup, takt desky 100 MHz a dva výstupy, hodiny 480 Hz a 0,5 MHz. Hodiny 480 Hz slouží k tomu, aby všechny LED diody na sedmisegmentovém displeji „svítily“současně rychlým přepínáním čtyř. Hodiny 0,5 MHz slouží k tomu, aby se stopky skutečně počítaly o centi-sekundy.

Krok 5: Zobrazovací modul

Tento zobrazovací modul má pět vstupů, 100MHz takt desky, dva hodiny z hodinového modulu a tlačítka start/stop a reset a dva výstupy, anody a katody. Tento modul má také „logiku“, jak stopky počítají, a obsahuje stroj s konečným stavem.

Krok 6: Vazebný modul

Tento poslední modul spojuje další dva moduly. Má tři vstupy, 100MHz takt desky a tlačítka start/stop a reset a dva výstupy, anody a katody. Hodiny 100 MHz jdou do modulu děliče hodin a modulu displeje a tlačítka start/stop a reset přejdou do modulu displeje. Výstupy modulu děliče hodin (480 Hz a 0,5 MHz) směřují ke dvěma hodinovým vstupům zobrazovacího modulu. Výstupy zobrazovacího modulu (anody a katody) jdou na výstupy konečného modulu.

Krok 7: Omezení

Dva vstupy mohou být libovolná tlačítka na desce FPGA Basys3 Atrix-7 FPGA a výstupy budou pro sedmisegmentový displej čtyři anody a osm katod (protože chcete také desetinnou čárku mezi sekundami a milisekundami).

Krok 8: Hotovo

Nahrajte program na desku Basys3 Atrix-7 FPGA a stopky spustíte stisknutím tlačítka start/stop!

Doporučuje:

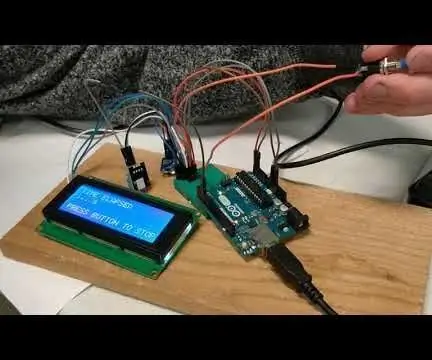

Jak vytvořit stopky pomocí Arduina: 8 kroků (s obrázky)

Jak vyrobit stopky pomocí Arduina: Jedná se o velmi jednoduché Arduino 16*2 LCD stopky s displejem ……….. Pokud se vám tento návod líbí, přihlaste se k odběru mého kanálu https://www.youtube.com /ZenoModiff

Základní stopky pomocí desky VHDL a Basys3: 9 kroků

Základní stopky pomocí desky VHDL a Basys3: Vítejte v instruktáži, jak vytvořit stopky pomocí základní desky VHDL a Basys 3. Jsme nadšeni, že s vámi můžeme sdílet náš projekt! Toto byl závěrečný projekt pro kurz CPE 133 (Digital Design) na Cal Poly, SLO na podzim 2016. Projekt, který jsme postavili

Jednoduché hodiny / stopky Arduino: 6 kroků (s obrázky)

Jednoduché hodiny / stopky Arduino: Tyto " instruktivní " v několika jednoduchých krocích vám ukáže a naučí vás, jak vyrobit jednoduché hodiny Arduino Uno, které také fungují jako stopky

Stopky na 30 m běh (Arduino): 6 kroků (s obrázky)

Stopky na 30 m běh (Arduino): Tento projekt byl vytvořen pro specifický účel ve finském baseballovém koučování a testování rychlosti juniorských hráčů v běhu na 30 m. Tento arduino projeckt byl také projektem kurzu v mých studiích. Projekt měl několik vzestupů a pádů, ale nyní alespoň funguje

Jednominutové stopky VHDL: 5 kroků

VHDL One Minute stopwatch: This is a tutorial on how to build a one minute stopwatch using VHDL and a Basys 3 board. Takové zařízení je ideální pro hry, kde každý hráč má maximálně jednu minutu na svůj tah. Stopky přesně zobrazují sekundy a milisekundy