Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:21.

- Naposledy změněno 2025-01-23 14:38.

V tomto pokynu se chystáme navrhnout SPI Bus Master od nuly ve VHDL.

Krok 1: Přehled SPI

- SPI je synchronní sériová sběrnice

- Jeho popularita a jednoduchost z něj dělaly de facto standard v sériové komunikaci

- Plně duplexní autobus

- Jednoduchý protokol a patří mezi nejrychlejší sériovou sběrnici

Krok 2: Specifikace návrhu

Toto jsou specifikace SPI Master, které navrhneme:

- Podporuje všechny čtyři režimy provozu; dynamicky konfigurovatelné

- Hodiny umožňují ovládání pro úsporu energie

- Staticky konfigurovatelná délka a rychlost slova

- Jedno přerušení pro vysílání i příjem

Krok 3: Rozjezd

Za prvé, naše IP by měla mít dvě rozhraní. Jedním z nich je sériové rozhraní a druhým je paralelní rozhraní. Sériové rozhraní se skládá z de facto standardních signálů SPI: MOSI, MISO, SS, SCLK.

MOSI se někdy nazývá SDO a MISO se někdy nazývá SDI.

Sériové rozhraní se používá ke komunikaci s externími periferiemi, tj. SPI slave.

Paralelní rozhraní se používá ke komunikaci s naším hostitelem, tj. Mikrokontrolérem nebo mikroprocesorem, který ve skutečnosti říká Masterovi, jaká data musí být sériově přenášena a přijímána prostřednictvím sériových linek. tj. všechny datové sběrnice patří do paralelního rozhraní.

Máme globální hodiny, které řídí interní logiku SPI, stejně jako SCLK, které generujeme interně.

Máme také některé řídicí signály, jako je povolení zápisu, povolení hodin. A přerušení a další stavové signály.

Protože se musíme vypořádat se složitými podmínkami řízení, je jednodušší navrhnout takové IP sériové komunikace jako FSM. SPI master navrhneme také jako FSM. FSM bude poháněno jinými interními hodinami, což je dvakrát SCLK. Že vnitřní hodiny jsou generovány pomocí synchronních čítačů z globálních hodin.

Všechny řídicí signály, které procházejí hodinovými doménami, mají synchronizátory, aby byly na bezpečnější straně.

Krok 4: RTL pohled na SPI hlavní jádro a průběhy simulace

Jedná se o čistý RTL design bez použití vyhrazených IP adres FPGA. Jedná se tedy o plně přenosný kód do jakéhokoli FPGA.

Doporučuje:

DRONE MASTER: 6 kroků

DRONE MASTER: Toto je tinkercad 3D design robota AI. Koordinace a ovládání všech dronů v programových nebo velkých funkcích nebo dokonce při fotbalových zápasech je docela obtížné. Na to potřebujeme více zkušených operátorů dronů. Ale tento robot AI je futuristický a bude

LCD displej I2C / IIC - Použijte SPI LCD na I2C LCD displej pomocí modulu SPI až IIC s Arduino: 5 kroků

LCD displej I2C / IIC | Použijte SPI LCD na I2C LCD displej pomocí modulu SPI až IIC s Arduino: Ahoj lidi, protože normální SPI LCD 1602 má příliš mnoho vodičů na připojení, takže je velmi obtížné propojit jej s arduino, ale na trhu je k dispozici jeden modul, který může převést SPI displej na IIC displej, takže pak potřebujete připojit pouze 4 vodiče

Design I2C Master ve VHDL: 5 kroků

Návrh I2C Master ve VHDL: V tomto návodu je pojednáno o návrhu jednoduchého I2C masteru ve VHDL. UPOZORNĚNÍ: kliknutím na každý obrázek zobrazíte celý obrázek

Design jednoduchého VGA řadiče ve VHDL a Verilog: 5 kroků

Návrh jednoduchého VGA řadiče ve VHDL a Verilogu: V tomto návodu navrhneme jednoduchý VGA řadič v RTL. VGA Controller je digitální obvod navržený pro řízení VGA displejů. Čte z vyrovnávací paměti snímků (paměť VGA), která představuje snímek, který má být zobrazen, a generuje potřebný

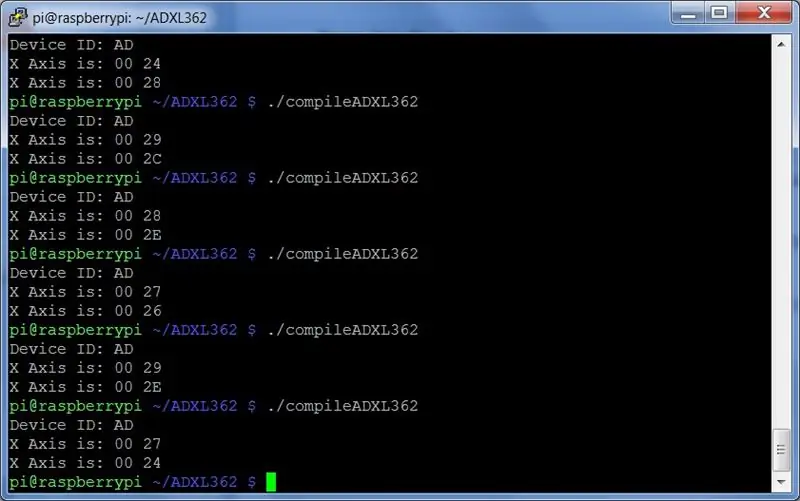

Předběžné* SPI na Pi: Komunikace s 3osým akcelerometrem SPI pomocí Raspberry Pi: 10 kroků

Předběžné* SPI na Pi: Komunikace pomocí 3osého akcelerometru SPI pomocí Raspberry Pi: Podrobný průvodce nastavením Raspbian a komunikace se zařízením SPI pomocí knihovny bcm2835 SPI (NE bit biteded!) To je stále velmi předběžné … Potřebuji přidat lepší obrázky fyzického připojení a zpracovat nějaký nešikovný kód