Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:21.

- Naposledy změněno 2025-01-23 14:38.

V tomto pokynu navrhneme jednoduchý VGA řadič v RTL. VGA Controller je digitální obvod navržený pro řízení VGA displejů. Čte z vyrovnávací paměti snímků (paměť VGA), která představuje zobrazovaný snímek, a generuje potřebná data a synchronizační signály pro účely zobrazení.

Pokud hledáte kód Verilog/System verilog: Navštivte můj blog VGA řadič a video systém ve Verilogu

Krok 1: Rozhraní řadiče VGA

Níže jsou uvedeny hlavní signály rozhraní v řadiči VGA

- Pixel Clock nebo VGA Clock

- Signály HSYNC a VSYNC

Pro zvolený VGA displej musíte nejprve vypočítat frekvenci Pixel Clock potřebnou k jeho pohonu. Záleží na 3 parametrech: Celkový počet horizontálních pixelů, Celkový počet vertikálních pixelů, Obnovovací frekvence obrazovky.

Obvykle F = THP * TVP * obnovovací frekvence

V přiloženém RAR najdete dokumentaci k taktování pixelů potřebnou pro různé VGA displeje.

Signály HSYNC a VSYNC jsou generovány z hodin Pixel. Načasování signálů HSYNC a VSYNC závisí na počtu parametrů: horizontální a vertikální frontporch, horizontální a vertikální backporch, horizontální a vertikální pixely zobrazení, horizontální a vertikální synchronizační šířky pulzů a polarity.

Tyto parametry jsou standardizovány pro vybraný VGA displej. Tyto dokumenty najdete v přiloženém RAR.

Tyto parametry jsou konfigurovatelné parametry v našem VGA řadiči IP.

Krok 2: Integrace řadiče VGA s displejem VGA

Obrázek ukazuje, jak integrovat VGA řadič s VGA displejem. K dokončení systému potřebujete další dvě součásti:

- Vyrovnávací paměť rámců: Paměť, která obsahuje rámeček, který se má zobrazit.

- Video DAC: DAC, který převádí digitální data RGB a pohání VGA displej analogovými signály RGB na odpovídající úrovni napětí.

Jeden z nejjednodušších a nejpopulárnějších video DAC je ADV7125. Jedná se o 8bitový DAC, který převádí digitální slova RGB na analogové signály 0-0,7 V a pohání VGA displej.

Krok 3: Návrh vyrovnávací paměti rámců

Je to paměť, která „ukládá“zobrazovaný obrázek. Obvykle je to RAM nebo někdy ROM. Budeme diskutovat o tom, jak navrhnout vyrovnávací paměť rámců, která bude představovat obrázek. Vyrovnávací paměť předává tyto digitální informace do Video DAC na příkaz z VGA řadiče.

Nejprve musíme určit potřebnou hloubku pixelů. Rozhoduje o kvalitě obrazu, rozmanitosti barev, které může pixel představovat. U 8bitového DAC musíme reprezentovat primární barevné komponenty pixelu: R, G a B po 8 bitech. To znamená, že pixel má 24 bitů.

Každý pixel je uložen souvisle v paměťových místech vyrovnávací paměti rámců.

Předpokládejme, že obrázek, který má být zobrazen, je 800x600 pixelů.

Proto je potřeba Frame Buffer 800x600 = 480000 x 24 bitů paměti

Celková velikost paměti je 800x600x24 = přibližně 1400 kB.

Pokud je černobílý obrázek, 800x600x1 = 60 kB přibližně.

Blokové paměti RAM mohou být použity k reprezentaci vyrovnávací paměti rámců v Xilinx FPGA.

Krok 4: Poznámky

- V závislosti na zvoleném DAC jsou na VGA řadiči potřeba další signály. Použil jsem ADV7125.

- Před spuštěním displeje VGA přidejte zpoždění cyklu pomocí žabek na VSYNC a HSYNC. Důvodem jsou latence DAC a paměti. Signály pixelů by měly být synchronizovány s HSYNC a VSYNC. V mém případě to bylo zpoždění 2 cyklů.

- Pokud nelze na FPGA navrhnout vyrovnávací paměť rámců dané velikosti z důvodu omezení velikosti bloku RAM, použijte menší paměť k reprezentaci obrázku a jednoduše upravte kód tak, aby se přesunul přes adresu na hranici dostupné paměti, nikoli na hranici celého rámce. To bude replikovat stejný obraz znovu a znovu po celé obrazovce. Další metodou je škálování pixelů, ve kterém je každý pixel replikován tak, aby zobrazoval celý obraz na celé obrazovce, v menším rozlišení. To lze provést vyladěním logiky inkrementace adres v kódu.

- IP je plně přenosný napříč všemi FPGA a je časově ověřen až do 100 MHz na Virtex-4 FPGA.

Krok 5: Připojené soubory

RAR obsahuje:

- Kód řadiče VGA

- PDF standardů VGA.

Doporučuje:

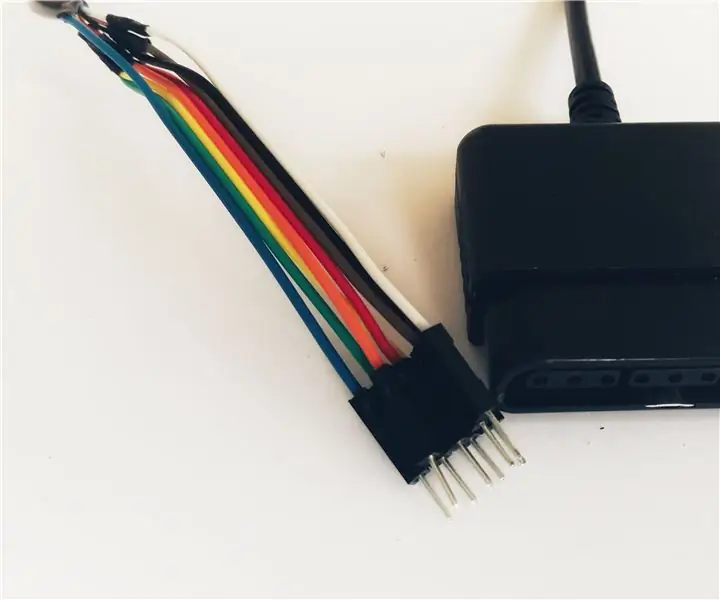

Adaptér Breakout řadiče PS2 pro propojení Arduino: 10 kroků

Adaptér Breakout řadiče PS2 pro propojení Arduino: Ovladač PlayStation 2 je opravdu užitečný gamepad pro robotické projekty. Je levný, hojně dostupný (z druhé ruky), obsahuje spoustu tlačítek a je kompatibilní s Arduino! Abyste jej mohli používat, potřebujete speciální konektor, který jej zapojí do

Návrh jednoduchého čtyřcestného řadiče asociativní mezipaměti ve VHDL: 4 kroky

Návrh jednoduchého čtyřcestného řadiče asociativní mezipaměti ve VHDL: V mém předchozím pokynu jsme viděli, jak navrhnout jednoduchý přímý mapovaný řadič mezipaměti. Tentokrát se posuneme o krok napřed. Budeme navrhovat jednoduchý čtyřcestný řadič asociativní mezipaměti. Výhoda? Méně chyb, ale za cenu perfo

Návrh programovatelného řadiče přerušení ve VHDL: 4 kroky

Návrh programovatelného řadiče přerušení ve VHDL: Jsem ohromen druhem odpovědí, které dostávám v tomto blogu. Díky, lidi, že jste navštívili můj blog a motivovali mě, abych se s vámi podělil o své znalosti. Tentokrát představím návrh dalšího zajímavého modulu, který vidíme ve všech SOC - Interrupt C

Návrh jednoduchého řadiče mezipaměti ve VHDL: 4 kroky

Návrh jednoduchého řadiče mezipaměti ve VHDL: Píši tento návod, protože jsem zjistil, že je trochu obtížné získat nějaký referenční kód VHDL, abych se naučil a začal navrhovat řadič mezipaměti. Navrhl jsem tedy řadič mezipaměti sám od nuly a úspěšně jej otestoval na FPGA. Mám p

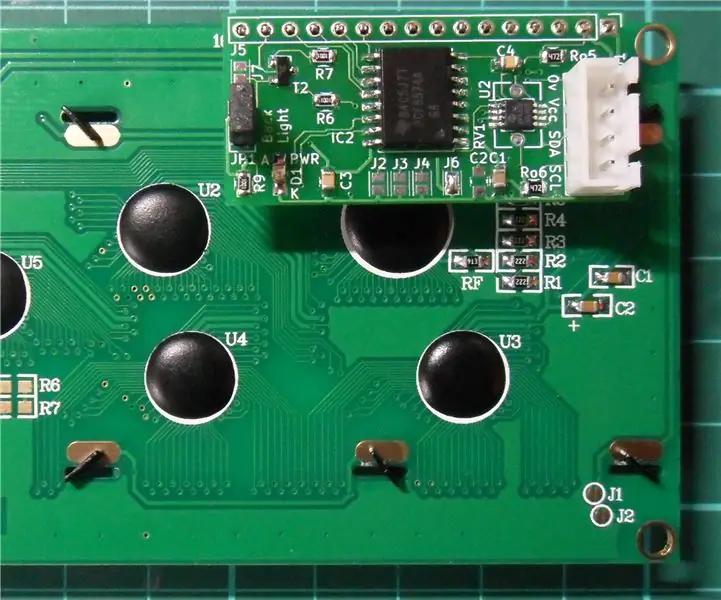

Modul řadiče LCD Uber I2C: 6 kroků

Modul řadiče LCD Uber I2C: Preamble Tento instruktáž podrobně popisuje, jak vytvořit modul ovladače na bázi LCD HD44780 (obrázek 1 výše). Modul umožňuje uživateli programově ovládat všechny aspekty LCD přes I2C, zahrnující; LCD a displej, kontrast a podsvícení zesiluje