Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:21.

- Naposledy změněno 2025-01-23 14:38.

V tomto pokynu je diskutován návrh jednoduchého I2C masteru ve VHDL.

POZNÁMKA: kliknutím na každý obrázek zobrazíte celý obrázek

Krok 1: Přehled sběrnice I2C

• Stojany pro integrovaný obvod Inter.

• Synchronní, poloviční duplex.

• Dvouvodičové rozhraní - SDA a SCL.

• SDA - sériová datová linka řízená Master a Slave

• SCL - Sériové hodiny generované Masterem

• Multi-master, Multi-slave protokol.

• Dva režimy - 100 kbit/s a 400 kbit/s: pomalý a rychlý.

Krok 2: Návrh RTL ve VHDL

Specifikace designu našeho I2C Master

- 8bitový datový rámec.

- Pouze jednosměrné ovládání SCL.

- 7bitová adresa slave.

- Podporuje pomalý i rychlý režim.

- Single Master, Multi-slave.

- Vyhovuje původním specifikacím I2C od společnosti Philips.

Používá se čistý RTL kód. IP je tedy snadno přenosný napříč všemi FPGA. Kompaktní design založený na FSM pomocí interně generovaných hodin zajišťuje optimální plochu a výkon.

Krok 3: Simulace a testování

Testovací prostředí

- Funkční simulace a testování pomocí Slave IP třetí strany.

- Syntetizováno pomocí sady nástrojů Xilinx Vivado.

- Implementováno a testováno na desce FPGA Artix-7.

- Časově ověřený design pro 100 MHz.

- Testované průběhy na DSO/CRO.

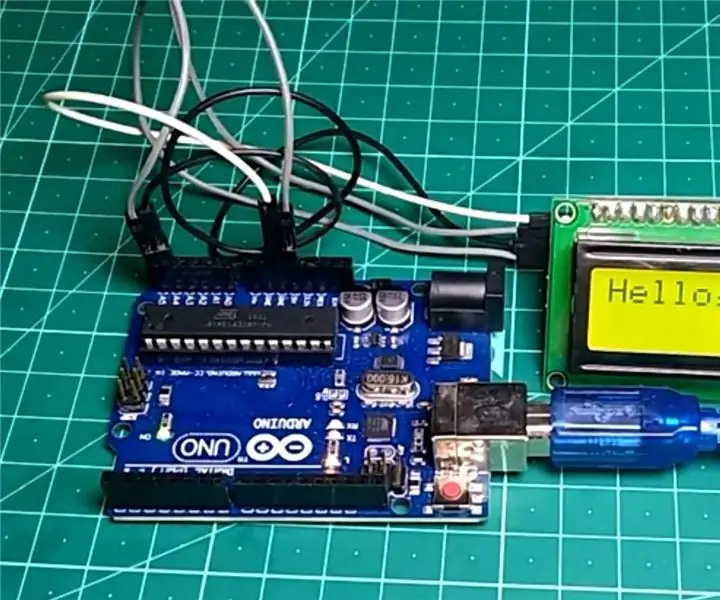

- Úspěšně testována komunikace s Arduino UNO jako I2C Slave.

Krok 4: Důležité poznámky

- Při testování Master pomocí I2C Slave IP nakonfigurujte podřízený kód podle svých požadavků. Možná budete chtít změnit výchozí frekvenci hodin a adresu slave. Taktovací frekvence by měla být nakonfigurována také v hlavním kódu.

- Při testování na palubě nezapomeňte na výsuvné odpory, protože SDA linka je společný odtokový výkon !!! Na Googlu zkontrolujte doporučený pull-up rezistor pro různé rychlosti i2c. Použil jsem 2,2K pro 100 kHz.

- Pokud nepoužíváte zkušební stolici a simulujete Master nezávisle, simulujte pečlivě signál SDA, protože se jedná o obousměrný signál (vstup). Má dva ovladače, hlavní a podřízený. Měli byste vědět, kdy „vynutit“a kdy „nevzdat“.

- SCL je jednosměrná linka. Není třeba tahat.

- Projděte si důkladně dokumentaci IP.

Krok 5: Připojené soubory

- Všechny RTL kódy I2C Master.

- Testovací stolice, kódy I2C Slave také pro testování.

- IP dokumentace.

V případě jakýchkoli dotazů mě neváhejte kontaktovat:

Mitu Raj

sledujte mě:

V případě dotazů kontaktujte: iammituraj@gmail.com

Doporučuje:

LCD displej I2C / IIC - Použijte SPI LCD na I2C LCD displej pomocí modulu SPI až IIC s Arduino: 5 kroků

LCD displej I2C / IIC | Použijte SPI LCD na I2C LCD displej pomocí modulu SPI až IIC s Arduino: Ahoj lidi, protože normální SPI LCD 1602 má příliš mnoho vodičů na připojení, takže je velmi obtížné propojit jej s arduino, ale na trhu je k dispozici jeden modul, který může převést SPI displej na IIC displej, takže pak potřebujete připojit pouze 4 vodiče

Design jednoduchého VGA řadiče ve VHDL a Verilog: 5 kroků

Návrh jednoduchého VGA řadiče ve VHDL a Verilogu: V tomto návodu navrhneme jednoduchý VGA řadič v RTL. VGA Controller je digitální obvod navržený pro řízení VGA displejů. Čte z vyrovnávací paměti snímků (paměť VGA), která představuje snímek, který má být zobrazen, a generuje potřebný

LCD displej I2C / IIC - Převeďte SPI LCD na I2C LCD displej: 5 kroků

LCD displej I2C / IIC | Převeďte SPI LCD na I2C LCD displej: použití spi lcd displeje vyžaduje příliš mnoho připojení, což je opravdu těžké, takže jsem našel modul, který dokáže převést i2c lcd na spi lcd, takže můžeme začít

Design SPI Master ve VHDL: 6 kroků

Návrh SPI Master ve VHDL: V tomto instruktážním návrhu navrhneme SPI Bus Master od nuly ve VHDL

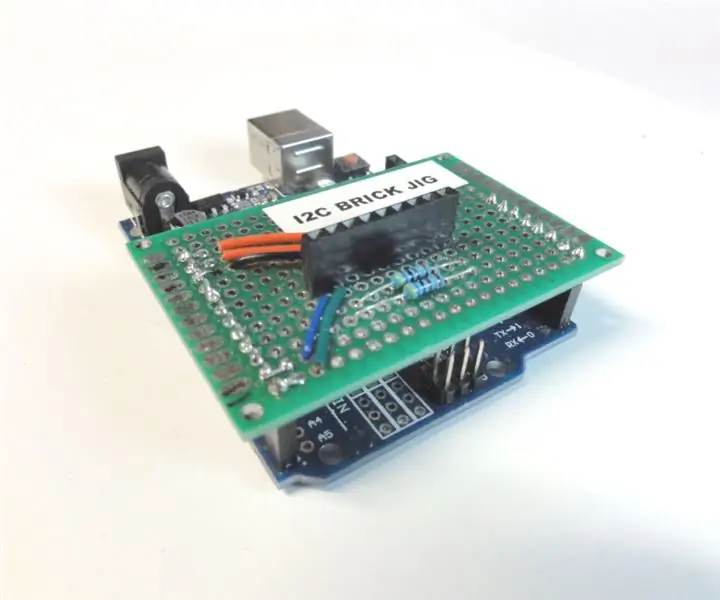

IOT123 - I2C BRICK MASTER JIG: 4 kroky

IOT123 - I2C BRICK MASTER JIG: Při vývoji ASSIMILATE SENSORS a ACTORS udržuji UNO po ruce pro odesílání příkazů adhoc I2C vyvíjeným prototypům. Jednou z výhod I2C BRICKS jsou standardizované vývody. Než používat pokaždé dráty na prkénko