Obsah:

- Krok 1: Fáze předpojatosti

- Krok 2: Rezistor snímající proud

- Krok 3: Zesilovač transvodivosti

- Krok 4: Zesilovač přístrojů

- Krok 5: Vstupní fáze a kalibrace

- Krok 6: Advanced Stuff: Spectral Leakage (DC)

- Krok 7: Pokročilé věci: Spektrální únik (AC)

- Krok 8: Advanced Stuff: theoretical Gain-factor

- Krok 9: Advanced Stuff: PA Shift

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:21.

- Naposledy změněno 2025-06-01 06:08.

Zajímal jsem se o výrobu bioimpedančního analyzátoru pro měření složení těla a při mých náhodných hledáních jsem našel návrh z třídy Biomedical Instrumentation 2015 z Vanderbilt University. Design jsem propracoval a mírně vylepšil. Rád bych se s vámi podělil o své poznatky. Vezměte si, co můžete použít z této „procházky“, pokud něco není jasné, navrhněte vylepšení. Možná někdy napíšu své myšlenky soudržnější formou, ale prozatím doufám, že můžete použít vše, co zde vidíte. (Pokud si myslíte, že to můžete napsat a zlepšit, jste vítáni)

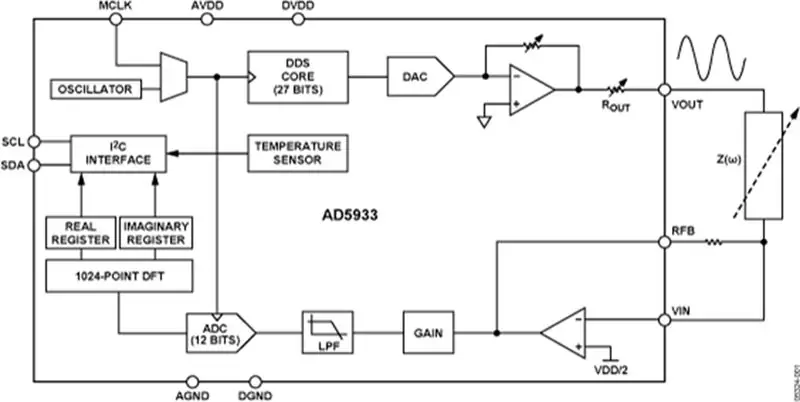

Teddy

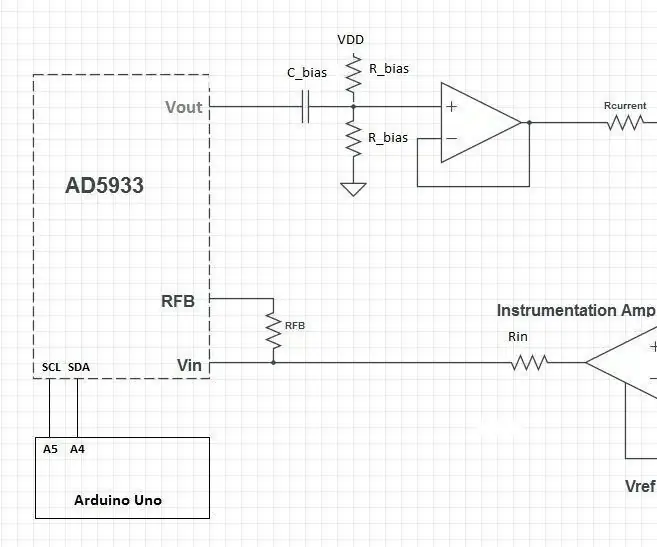

Tento design se skládá z čipu AD5933 a vlastního analogového front-endu (AFE) pro propojení AD5933 s tělem. AD5933 poté provede měření a výsledky pak může zpracovat mikrokontrolér (např. Arduino).

Pokud plánujete používat Arduino jako napájecí zdroj, ujistěte se, že operační a přístrojové zesilovače (operační zesilovače a zesilovače) podporují takzvaná napětí „jednoho napájení“a mají specifikaci rail-to-rail.

(V následujícím textu budu používat napájecí zdroj (z Arduina) 5 V a nastavení rozsahu 1 na AD5933.)

Krok 1: Fáze předpojatosti

První část AFE je fáze předpětí. Signál výstupního napětí není vystředěn uprostřed rozsahu napájecího napětí (VDD/2). To je napraveno použitím kondenzátoru k zablokování stejnosměrné části signálu a jeho odesláním přes rozdělovač napětí pro přidání stejnosměrného offsetu zpět do signálu.

Dva odpory opětovného předpětí mohou mít libovolnou hodnotu, pokud jsou stejné. Specifická hodnota limitu také není důležitá.

Fáze opětovného vychýlení funguje jako horní propust, a proto má mezní frekvenci:

f_c = 1 / (2 * pi * (0,5 * R) * C)

Ujistěte se, že mezní frekvence je o několik desetiletí nižší než minimální frekvence, kterou plánujete používat. Pokud plánujete ve své aplikaci používat 1kHz, měli byste použít hodnoty Caps a Resistor, které vám poskytnou mezní frekvenci řádově 1-10 Hz.

Poslední částí této fáze je operační zesilovač nastavený jako sledovač napětí. To má zajistit, aby hodnoty odporu nerušily další fázi

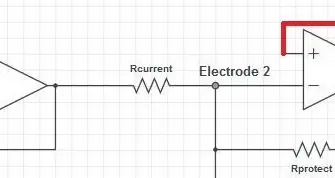

Krok 2: Rezistor snímající proud

První částí další fáze je odpor snímající proud. Proud procházející tímto rezistorem bude stejný proud, jaký se zesilovač pokusí udržet tělem. Ujistěte se, že proud odpovídá bezpečnostním normám IEC6060-1*:

Pod frekvencemi 1 kHz je tělem povoleno maximálně 10 mikroAmpérů (RMS). Při frekvencích nad 1kHz udává následující rovnice maximální povolený proud:

Maximální střídavý proud <(minimální frekvence v kHz) * 10 mikroAmpérů (RMS)

Vztah mezi špičkovou amplitudou signálu AC a jeho hodnotou RMS je: Peak = sqrt (2) * RMS. (10 mikroAmps RMS odpovídá špičkové amplitudě 14 mikroAmps)

Pomocí Ohmova zákona na odporu můžeme vypočítat hodnotu odporu, která bude vyhovovat bezpečnostnímu standardu. Používáme budicí napětí z AD5933 a maximální hodnotu proudu:

U = R * I => R = U / I

Např. pomocí nastavení rozsahu 1 Upeak = 3V / 2 = 1,5V (nebo 1V @3,3V)

Pomocí špičkové hodnoty 14 mikroAmp shora získám hodnotu odporu nejméně 107 kOhms

Reference:

* Analog Devices: „Bioimpedance Circuit Design for Body Worn Systems“

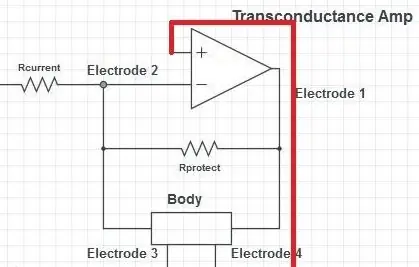

Krok 3: Zesilovač transvodivosti

Za proudovým snímacím odporem je operační zesilovač v konfiguraci negativní zpětné vazby. Jedná se o takzvané nastavení Load-in-the-Loop. Pozitivní vstupní svorka operačního zesilovače je připojena k napětí VDD/2. Operační zesilovač se nyní pokusí upravit svůj výstup v opačném směru než budicí signál tak, aby napětí na záporném pólu bylo stejné jako VDD/2. To vytvoří potenciál houpání tlačením a tažením proudu tělem.

Proud odebíraný ze záporného pólu operačního zesilovače je prakticky nulový. Veškerý proud procházející rezistorem snímajícím proud proto musí protékat tělem. Toto je mechanismus, který z tohoto nastavení dělá zesilovač trans-konduktance (také nazývaný napěťově řízený zdroj proudu, VCCS).

Operační zesilovač může udržovat proud pouze v případě, že impedance těla není příliš vysoká. Jinak by výstup operačního zesilovače dosáhl maxima při napájecím napětí (0 nebo 5 V). Maximální rozsah napětí, který lze udržovat, je VDD/2 + Upeak (2,5 + 1,5 V = 4 V při napájení 5 V). Okraje napětí operačního zesilovače by měly být odečteny od této hodnoty, ale pokud má operační zesilovač specifikace rail-to-rail, bylo by to jen malé množství. Maximální impedance, kterou může operační zesilovač řídit, je tedy:

Z <(VDD / 2 + Upeak) / Imax

(V mém nastavení Z <4V / 14 mikroAmps = 285 kOhms, přání je dost na pokrytí rozsahu impedance těla)

Rezistor chrániče má velmi velkou hodnotu (1-1,5 MOhms) ve srovnání s tělem (přibližně 100kOhms) a pro všechny běžné operace to nebude odebírat žádný znatelný proud a impedanci paralelního připojení dominuje impedance těla. Pokud by se měla zvýšit impedance těla (např. Uvolňující se polštářky), pak může proud procházet rezistorem a max. Výstup z operačního zesilovače by v elektrodách nevytvářel nepříjemné napětí.

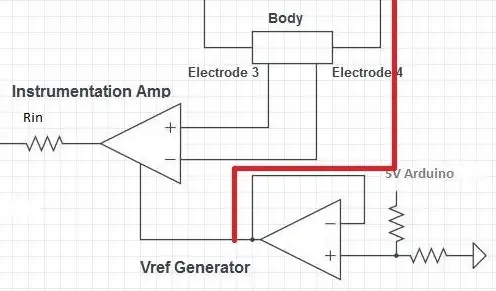

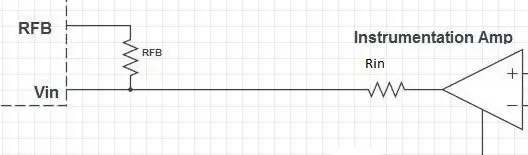

Krok 4: Zesilovač přístrojů

Další fází je přístrojový zesilovač (in-amp), který měří napětí na celém těle. Napětí na celém těle osciluje kolem 0V, ale AD5933 potřebuje, aby vstupní napětí bylo v kladném rozsahu. In-amp proto přidává k měřenému napěťovému signálu stejnosměrný offset VDD/2.

Reference VDD/2 je generována děličem napětí. Lze použít jakýkoli hodnotový odpor, pokud jsou stejné. Dělič napětí je oddělen od impedance zbytku obvodů sledovačem napětí. Výstup sledovače napětí lze poté předat jak zesilovači in-amp, tak trans-konduktantnímu zesilovači.

Krok 5: Vstupní fáze a kalibrace

Vstupní stupeň AD5933 obsahuje operační zesilovač v konfiguraci negativní zpětné vazby. Existují dva odpory: jeden v sérii (Rin) a jeden paralelně (RFB). Zisk operačního zesilovače je dán vztahem

A = - RFB / Rin

Zisky vstupního operačního zesilovače a vstupního zesilovače (a PGA) musí zajistit, aby signál přicházející do ADC AD5933 byl vždy v rozmezí 0 V a VDD.

(Používám hodnoty zesílení jednotky a odporu a hodnoty odporu, které dávají přibližně A = 0,5)

Uvnitř AD5933 převede ADC napěťový signál na a na digitální signál. Rozsah napětí od 0V do VDD je převeden na digitální rozsah 0-128 (2^7). (Dokumentace v tom není jasná, ale podrobné prozkoumání zápletek v [1] a některé experimenty z mé strany to potvrzují.)

Uvnitř DFT modulu je další škálování 256 (1024/4, viz [1]), než je výsledek uložen do skutečného a imaginárního registru.

Sledováním napěťového signálu skrz AFE do ADC a použitím faktorů měřítka uvedených výše je možné odhadnout faktor zisku jako:

g = (VDD * Rcurrent * Rin) / (256 * PGA * Upeak * RFB * 2^7)

nějaká kalibrace může být stále nezbytná, takže vezměte v úvahu některé efekty, které nejsou součástí tohoto matematického modelu, proto prosím změřte skutečnou hodnotu zisku měřením složek známé impedance, jako jsou odpory. (g = Z / mag, viz níže)

Impedanci lze nyní vypočítat podle

Z = g * mag

mag = sqrt (skutečný^2 + imaginární^2)

PA = arctan2 (skutečný, imaginární) - deltaPA

PA je pravděpodobně nutné kalibrovat a v AD5933 je systematický fázový posun v závislosti na frekvenci. deltaPA bude pravděpodobně nějaká lineární funkce frekvence.

Odpor a reaktanci lze nyní vypočítat pomocí

R = Z * cos (PA)

X = Z * sin (PA)

Reference: [1] Leonid Matsiev, „Zlepšení výkonu a univerzálnosti systémů založených na jednofrekvenčních DFT detektorech, jako je AD5933“, Electronics 2015, 4, 1-34; doi: 10,3390/elektronika4010001

Krok 6: Advanced Stuff: Spectral Leakage (DC)

Signál, který jsme vložili do AD5933, je napětí/proud jako funkce času, ale naším hlavním zájmem je impedance jako funkce frekvence. K převodu mezi časovou a frekvenční doménou musíme provést Fourierovu transformaci signálu časové domény. AD5933 má vestavěný modul diskrétní Fourierovy transformace (DFT). Při nízkých frekvencích (pod přibližně 10 kHz) je tvorba DFT ovlivněna aliasingem a spektrálními úniky. V [1] prochází matematikou, jak opravit spektrální únik. Podstatou toho je vypočítat pět (plus dvě) konstanty pro každý frekvenční krok v rozmítání. To lze snadno provést např. softwarově Arduino.

Únik se vyskytuje ve dvou formách: stejnosměrný únik, který je v přírodě aditivní, a únik střídavého proudu, který má v přírodě multiplikativní charakter.

Únik stejnosměrného proudu pramení ze skutečnosti, že napěťový signál u ADC nekmitá kolem 0 V, ale kolem VDD/2. Úroveň stejnosměrného proudu VDD/2 by měla odpovídat digitálnímu stejnosměrnému čtení přibližně 64 (označeno delta v [1]).

Kroky k nápravě DC spektrálního úniku:

1) Vypočítejte faktor obálky E pro aktuální frekvenci.

2) Vypočítejte dva faktory zisku GI (skutečné) a GQ (imaginární)

3) Odečtěte delta * GI od hodnoty skutečného registru a delta * GQ od hodnoty imaginárního registru

Reference:

[1] Leonid Matsiev, „Zlepšení výkonu a univerzálnosti systémů založených na

Jednofrekvenční DFT detektory jako AD5933 , Electronics 2015, 4, 1-34; doi: 10,3390/elektronika4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, „jednoduchý širokopásmový impedanční měřič založený na integrovaném obvodu AD5933“, Metrol. Měření Syst., Sv. XXII (2015), č. 1, s. 13-24.

Krok 7: Pokročilé věci: Spektrální únik (AC)

Stejně jako únik stejnosměrného proudu lze i únik střídavého proudu opravit matematicky. V [1] se odpor a reaktance nazývají A*cos (phi) respektive A*sin (phi), kde A odpovídá velikosti impedance a phi odpovídá fázovému úhlu (PA).

Kroky k nápravě spektrálního úniku AC:

1) Vypočítejte faktor obálky E (ne stejný jako pro DC) pro aktuální frekvenci.

2) Vypočítejte tři faktory a, b a d. (přibližné hodnoty při vyšších frekvencích: a = d = 256 a b = 0)

3) Odpor (Acos (phi)) a reaktanci (Asin (phi)) lze nyní vypočítat v digitálních jednotkách

Reference: [1] Leonid Matsiev, „Zlepšení výkonu a univerzálnosti systémů založených na jednofrekvenčních DFT detektorech, jako je AD5933“, Electronics 2015, 4, 1-34; doi: 10,3390/elektronika4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, „jednoduchý širokopásmový impedanční měřič založený na integrovaném obvodu AD5933“, Metrol. Měření Syst., Sv. XXII (2015), č. 1, s. 13-24.

Krok 8: Advanced Stuff: theoretical Gain-factor

Vzhledem k matematickému modelování DFT by mělo být také možné modelovat celý AFE matematicky. Matematicky lze napěťový signál popsat pomocí sinusové funkce s danou pevnou frekvencí, stejnosměrným offsetem a střídavou oscilací se špičkovou amplitudou. Frekvence se během kroku frekvence nemění. Protože faktor zisku mění pouze velikost impedance a ne PA, nebudeme se zde zabývat žádným fázovým posunem indukovaným na signálu.

Zde je krátké shrnutí napěťového signálu, který se šíří AFE:

1) Po fázi opětovného předpětí je amplituda střídavého proudu stále Upeak = 1,5 V (1 V @ VDD = 3,3 V) a DC offset byl změněn na VDD/2.

2) V rezistoru snímajícím proud je napětí stále stejné jako v předchozím stupni …

3)… ale vzhledem k houpacímu napětí operačního zesilovače mají střídavé oscilace velikost Z*Upeak/Rcurrent. (DC offset je zrušen referenčním napětím operačního zesilovače VDD/2 - otočný bod houpačky - a v této části obvodu se stává virtuálním uzemněním)

4) Jednotkový zesilovač přidává DC offset VDD/2 zpět a předává signál do vstupního stupně AD5933

5) Operační zesilovač ve vstupním stupni má zisk A = -RFB/Rin a amplituda střídavého proudu se proto stává (Z*Upeak/Rcurrent)*(RFB/Rin)

6) Těsně před ADC je programovatelný zesilovač zisku (PGA) se dvěma nastaveními zisk 1 nebo 5. Napěťový signál v ADC se tedy stává: PGA*(Z*Upeak/Rcurrent)*(RFB/Rin)

ADC převádí signál v (t) na digitální signál x (t) = u (t) / VDD * 2^7 s 12bitovou přesností.

Velikost A je připojena k impedanci Z faktorem zisku, k, jako A = k * Z a má přibližně hodnotu k = PGA * Upeak * RFB * 2^7 / (VDD * Rcurrent * Rin).

Pokud chcete místo toho pracovat s faktorem zisku g = 1 / k a Z = g * A.

Krok 9: Advanced Stuff: PA Shift

V [2] shledávají systematický posun v PA jako funkci frekvence. To je způsobeno časovým zpožděním mezi DAC, kde je generován budicí signál, a DFT, kde je třeba spojit přicházející signál s odchozím signálem.

Posun je charakterizován počtem hodinových cyklů, kdy je signál zpožděním mezi DAC a DFT interně v AD5933.

Reference: [1] Leonid Matsiev, „Zlepšení výkonu a univerzálnosti systémů založených na jednofrekvenčních DFT detektorech, jako je AD5933“, Electronics 2015, 4, 1-34; doi: 10,3390/elektronika4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, „jednoduchý širokopásmový impedanční měřič založený na integrovaném obvodu AD5933“, Metrol. Měření Syst., Sv. XXII (2015), č. 1, s. 13-24.

Doporučuje:

Analýza LTE Cat.M1 PSM (úsporný režim): 4 kroky

Analýza LTE Cat.M1 PSM (úsporný režim): V předchozím článku jsme diskutovali o tom, jak nastavit cyklus Active / Sleep pomocí PSM. Vysvětlení nastavení hardwaru a PSM a příkazu AT najdete v předchozím článku. (Odkaz: https://www.instructables.com/id/What-Is-a-PSMPow…Ac

Analýza teplot/vlhkosti pomocí Ubidots a Google-Sheets: 6 kroků

Analýza dat teploty/vlhkosti pomocí Ubidots a Google-Sheets: V tomto tutoriálu změříme různé údaje o teplotě a vlhkosti pomocí snímače teploty a vlhkosti. Dozvíte se také, jak tato data odeslat do Ubidots. Takže jej můžete analyzovat odkudkoli pro různé aplikace. Také zasláním

Analýza hlavních komponent: 4 kroky

Principal Component Analysis: Principal Component Analysis je statistická metoda, která pomocí ortogonálních transformací převádí sadu případně korelovaných proměnných na sadu lineárně nekorelovaných hodnot. Jednoduše řečeno, vzhledem k datové sadě s více dimenzemi pomáhá

Analýza knihy objednávek pomocí barevného senzoru: 14 kroků

Analýza knihy objednávek pomocí barevného senzoru: Používá červený/zelený/modrý barevný senzor Adafruit TCS34725 k analýze světelného výstupu z knihy objednávek na obrazovce při obchodování s kryptoměnami. Pokud převážně „kupujete“přicházejí objednávky, reprezentované zelenými čísly na obrazovce, můžete očekávat

Analýza systému Windows Bluetooth - přístup SensorTag: 7 kroků (s obrázky)

Windows Bluetooth System Analysis - přístup SensorTag: V následujícím textu udělám analýzu operačního systému Windows (OS) z pohledu komunikace se zařízeními Bluetooth Low Energy - v našem případě s různými typy SensorTags: Thunderboard React, Thunderboard Sense (b