Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:21.

- Naposledy změněno 2025-01-23 14:38.

Jsem ohromen tím, jaké reakce na tento blog dostávám. Díky, lidi, že jste navštívili můj blog a motivovali mě, abych se s vámi podělil o své znalosti. Tentokrát představím návrh dalšího zajímavého modulu, který vidíme ve všech SOC - Interrupt Controller.

Navrhneme jednoduchý, ale výkonný programovatelný řadič přerušení. Jedná se o zcela konfigurovatelný a parametrizovaný design, který je přenosný napříč platformami. Navrhl jsem to poté, co jsem hodně četl na některých populárních architekturách řadičů přerušení, jako jsou NVIC, 8259a, RISC-V PLIC, Microblaze's INTC atd. Doufám, že vám tento blog pomůže, a pomůže vám získat představu o tom, jak přerušení řeší procesor pomocí ovladače přerušení.

Krok 1: Specifikace

Níže jsou uvedeny specifikace IP:

- Rozhraní AHB3-Lite.

-

Staticky konfigurovatelné parametry:

- Počet externích zdrojů přerušení; podporuje až 63 přerušení.

- Počet úrovní priority; podporuje až 63 úrovní.

- Počet úrovní vnoření; podporuje až 8 úrovní vnoření.

- Šířka autobusu; 32 nebo 64.

- Globálně a lokálně maskovatelná přerušení.

- Dynamicky konfigurovatelná úroveň priority pro každé přerušení.

- Dva režimy provozu - plně vnořený režim a režim stejné priority.

- Podporuje přerušení citlivá na aktivní úroveň.

Při návrhu je použit mechanismus rušení rušení inspirovaný specifikacemi RISC-V PLIC.

Prevence předčasného přerušení je inspirována číslem 8259a

Další čtení: Microblaze INTC, NVIC

Krok 2: Přehled PIC

Programovatelný řadič přerušení (PIC) přijímá více přerušení od externích periferií a sloučí je do jednoho výstupu přerušení do jádra cílového procesoru.

PIC je řízen prostřednictvím kontrolních a stavových registrů. Všechny registry PIC jsou mapovány do paměti a jsou přístupné prostřednictvím sběrnicového rozhraní AHB3-Lite.

Banka registrů se skládá z konfiguračního registru, aktivačních registrů, čekajících registrů, registrů v provozu, prioritních registrů a registru ID, které jsou typické pro řadiče přerušení.

Konfigurační registr slouží k nastavení režimu provozu PIC. Může pracovat buď v plně vnořeném režimu, nebo v režimu stejné priority.

Každému přerušení lze přiřadit priority a jednotlivě maskovat. Podporováno je také globální maskování všech přerušení.

Registrační banka spolupracuje s prioritním řešením a BTC (Binary-Tree-Comparator), aby vyřešila priority čekajících přerušení a odpovídajícím způsobem potvrdila přerušení procesoru. Registr ID obsahuje ID čekajícího přerušení s nejvyšší prioritou.

Krok 3: Návrh a implementace RTL

Návrhový důraz společnosti PIC na snížení latence řešení priorit, což je nejvíce kritická část návrhu. Vzhledem k tomu, že design řeší priority v jediném hodinovém cyklu, výkon klesá s nárůstem počtu zdrojů se složitostí Log2.

Návrh byl úspěšně implementován a načasování ověřeno až na následující frekvence na FPGA Artix-7.

- Až 15 zdrojů: 100 MHz

- Až 63 zdrojů: 50 MHz

Latence přerušení přidaná samotným PIC jsou 3 hodinové cykly (s výjimkou doby přepnutí kontextu procesoru a doby načítání první instrukce ISR).

Krok 4: Důležité poznámky a připojené soubory

Důležité poznámky:

- Pokud je rozhraní AHB3-Lite nežádoucí, můžete změnit horní modul a použít kostru PIC. Poskytovaná zkušební lavice je však pro IP s rozhraním AHB3-Lite.

- PIC IP v1.0 je zcela přenosný, holý RTL design.

- Funkčně ověřeno, aby fungovalo v obou režimech.

Přiložené soubory:

- Navrhněte kódy a testovací stůl ve VHDL.

- Úplná dokumentace IP.

Jedná se o open-source design … Neváhejte použít …

V případě jakýchkoli dotazů kdykoli:

Mitu Raj

Doporučuje:

Návrh jednoduchého čtyřcestného řadiče asociativní mezipaměti ve VHDL: 4 kroky

Návrh jednoduchého čtyřcestného řadiče asociativní mezipaměti ve VHDL: V mém předchozím pokynu jsme viděli, jak navrhnout jednoduchý přímý mapovaný řadič mezipaměti. Tentokrát se posuneme o krok napřed. Budeme navrhovat jednoduchý čtyřcestný řadič asociativní mezipaměti. Výhoda? Méně chyb, ale za cenu perfo

Návrh jednoduchého řadiče mezipaměti ve VHDL: 4 kroky

Návrh jednoduchého řadiče mezipaměti ve VHDL: Píši tento návod, protože jsem zjistil, že je trochu obtížné získat nějaký referenční kód VHDL, abych se naučil a začal navrhovat řadič mezipaměti. Navrhl jsem tedy řadič mezipaměti sám od nuly a úspěšně jej otestoval na FPGA. Mám p

Design jednoduchého VGA řadiče ve VHDL a Verilog: 5 kroků

Návrh jednoduchého VGA řadiče ve VHDL a Verilogu: V tomto návodu navrhneme jednoduchý VGA řadič v RTL. VGA Controller je digitální obvod navržený pro řízení VGA displejů. Čte z vyrovnávací paměti snímků (paměť VGA), která představuje snímek, který má být zobrazen, a generuje potřebný

Návrh UART ve VHDL: 5 kroků

Design UART in VHDL: UART znamená Universal Asynchronous Receiver Transmitter. Je to nejpopulárnější a nejjednodušší sériový komunikační protokol. V tomto návodu se naučíte, jak navrhnout modul UART ve VHDL

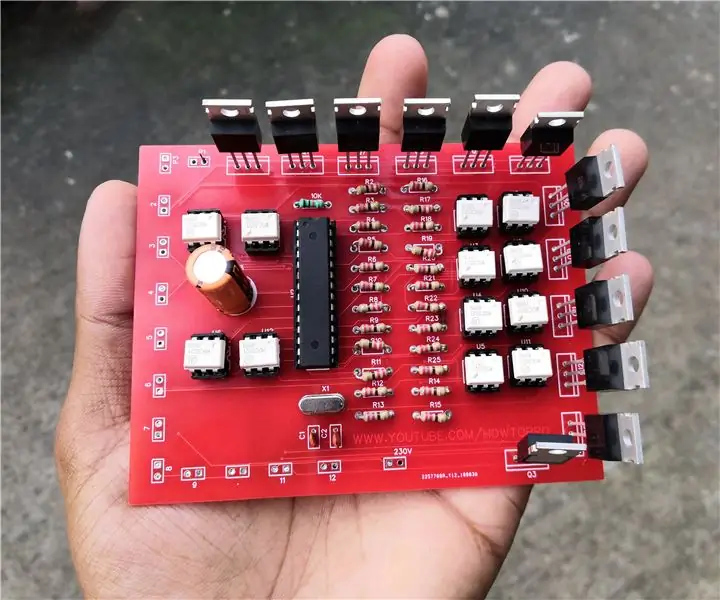

DIY masivní nastavení 12 000 wattů 230v programovatelného osvětlení 12 kanálů: 10 kroků

DIY Masivní nastavení 12 000 wattů 230v programovatelného osvětlení 12kanálový: Dobrý den všem, v tomto projektu vám ukážu, jak lze vyrobit masivní 12 000 wattový LED světelný ovladač. Toto je 12kanálové nastavení, pomocí tohoto obvodu můžete ovládat jakékoli 230v světlo .Můžete vytvořit různé vzory osvětlení. V tomto videu jsem