Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:20.

- Naposledy změněno 2025-01-23 14:38.

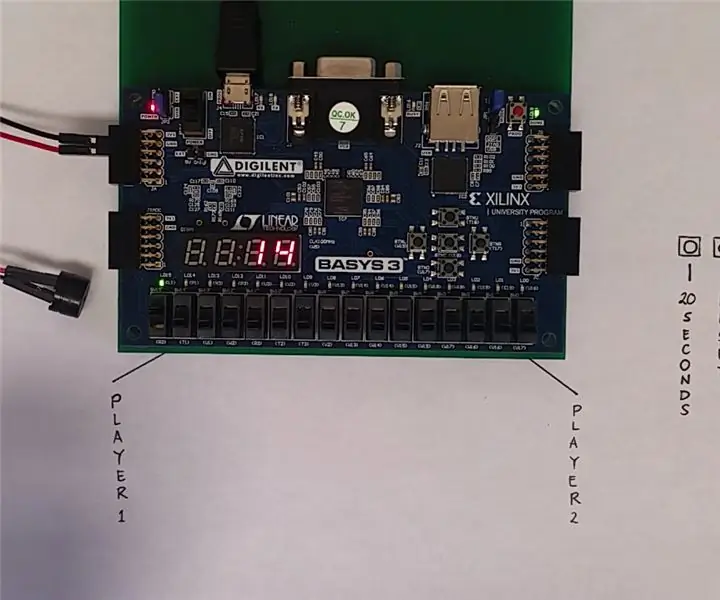

Konkurenční bzučákový systém navržený v tomto projektu funguje podobně jako bzučákové systémy používané v regionálních a národních soutěžích Bowl Science. Tento projekt byl inspirován mým zapojením do vědeckého týmu mé střední školy po dobu tří let. Vždy jsme toužili obnovit systém blokovacího bzučáku pomocí 5sekundového a 20sekundového časovače.

Aby poskytly určité znalosti o systému bzučáků, jsou bzučáky vědecké mísy naprogramovány tak, aby zadávaly maximálně 8 hráčů (s 8 samostatnými bzučáky). Po stisknutí jednoho bzučáku se rozsvítí bzučák první osoby, který indikuje, který hráč obdrží otázku. Zbytek hráčů bude „zablokován“, což znamená, že jejich bzučáky nebudou reagovat, dokud moderátor nezruší systém bzučáku.

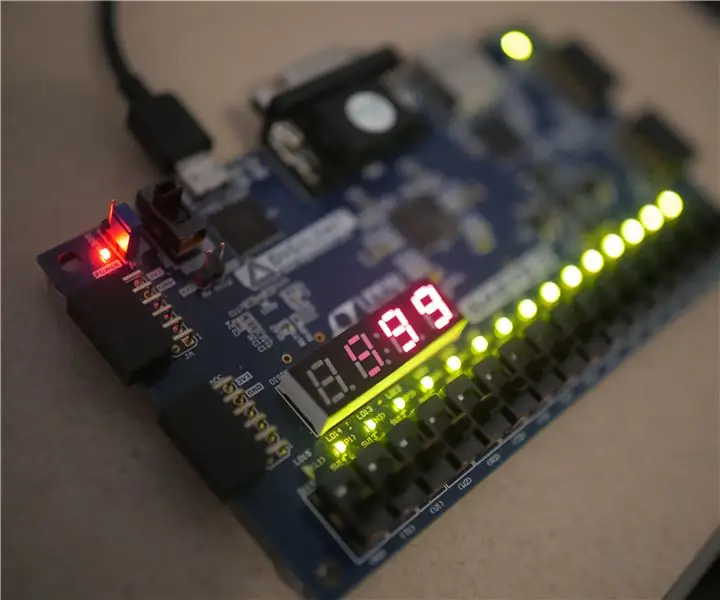

Poté, co moderátor přečte otázky, stisknutím tlačítka spustí časovač odpočítávání, který se zobrazí na sedmisegmentovém displeji. Po otázce „přehození“může moderátor stisknutím pravého tlačítka spustit odpočítávání od 5 sekund. Mezitím po „bonusové“otázce může moderátor stisknutím levého tlačítka spustit odpočítávání od 20 sekund. Jakmile časovač dosáhne nuly, zvukový bzučák oznámí, že hráči vypršel čas.

Chcete -li resetovat systém a časovač odpočítávání, může moderátor stisknout středové tlačítko. Pro resetování blokovacího mechanismu a LED diod přehrávače musí být spínače pro hráče 1 a hráče 2 na nízké úrovni.

Krok 1: Materiály

Budete potřebovat následující:

- Deska Basys3 (nebo ekvivalentní deska FPGA)

- Micro-B USB kabel

- Reproduktor (použil jsem pasivní reproduktor)

- 2 dráty

- Software k implementaci na FPGA (použil jsem Vivado)

- Soubor systému Competitive Buzzer System

Krok 2: Diagram černé skříňky

Schéma černé skříňky ukazuje vstupy a výstupy, které budou použity v tomto systému bzučáku.

VSTUPY:

player1, player2 Tyto vstupy jsou připojeny ke dvěma přepínačům na desce Basys3. Pro pohodlí budou použity přepínače úplně vlevo a vpravo.

resetovat Středové tlačítko bude sloužit k reprezentaci resetovacího tlačítka.

count_down_20_sec Levé tlačítko bude představovat tlačítko 20sekundového časovače.

count_down_5_sec Pravé tlačítko bude představovat tlačítko 20sekundového časovače. Abyste zajistili spuštění 20sekundového i 5sekundového časovače, podržte tlačítko, dokud sedmisegmentový displej nezobrazí časovač.

CLK Deska FPGA bude generovat hodiny, které běží s frekvencí 10 ns.

VÝSTUPY:

reproduktor Výstup reproduktoru je připojen k externímu bzučáku nebo reproduktoru. Reproduktor budete muset připojit k portům JA pmod na desce Basys3. Tento krok bude popsán níže.

reproduktor_LED Tento výstup je připojen k LED ve středu desky a bude pouze indikovat, když je výstup reproduktorů FPGA vysoký. Můžete to použít k testování externího reproduktoru. Některé porty pmod nemusí fungovat správně, takže můžete vyzkoušet jiné a pomocí LED kontrolovat, zda by měl být reproduktor zapnutý.

SEGMENTY Tento výstup je připojen k osmi jednotlivým segmentům na sedmisegmentovém displeji včetně desetinné čárky.

DISP_EN Tento výstup je připojen ke čtyřem anodám na sedmisegmentovém displeji.

player_LED Tento výstup je 2-svazkový signál, který je připojen k LED nad přepínači player1 a player2. První hráč, který otočí svůj odpovídající spínač, bude indikován LED diodou. Všimněte si, že obě LED diody nemohou svítit současně.

Krok 3: Připojení externího reproduktoru

Chcete -li připojit externí reproduktor k desce Basys3, vezměte dva kabely a připojte je podle obrázku nahoře. Bílá čára spojuje záporný pól reproduktoru s uzemňovacím portem na desce. Červená čára spojuje kladný terminál reproduktoru s portem JA10 pmod na desce.

Soubor omezení je navržen tak, aby fungoval jakýkoli port od JA1 do JA10. Některé piny na desce však nereagují, takže pokud JA10 nefunguje, můžete zkusit ostatní porty.

Krok 4: Strukturální diagram

Obrázek výše ukazuje strukturální diagram konkurenčního bzučákového systému včetně všech komponent, které tvoří hlavní modul. Jejich popisy jsou následující:

player_lockout_LED1 LED kontrolka uzamčení přehrávače je stroj s konečným stavem, který používá kódování jedním spuštěním. Má čtyři vstupy: player1, player2, reset a CLK. Obsahuje výstup 2bitového balíčku player_LED. Vstupy a výstupy komponenty player_lockout_LED1 jsou přímo připojeny ke stejně pojmenovaným vstupům a výstupům hlavního modulu.

buzzer_tone1 Komponenta bzučáku je založena na tomto kódu zveřejněném na fóru

stackoverflow.com/questions/22767256/vhdl-… Byl však upraven tak, aby vydával souvislý zvuk s frekvencí 440 Hz (poznámka). Vstup povolení je připojen k signálu bzučáku_povoleného, který je výstupem komponenty down_counter_FSM1.

clk_div1 Součást oddělovače hodin je upravená verze rozdělovače hodin profesora Bryana Mealyho poskytovaného na PolyLearn. Zpomaluje hodiny, takže výstupní perioda je 1 sekunda.

down_counter_FSM1 Down counter je FSM navržený tak, aby odpočítával až na nulu. Dva možné časy spuštění jsou 20 nebo 5, které zvolí uživatelský vstup. Když časovač dosáhne nuly, vydá „1“, což znamená, že čas vypršel. Tento výstup funguje jako povolení pro komponentu bzučáku. Počitadlo také vydává signál 8bitového svazku, který odesílá 8bitový BCD, který je odeslán do segmentového dekodéru. Dalším výstupem je counter_on, který je také připojen k platnému vstupu na segmentovém dekodéru.

sseg_dec1 Komponenta sedmisegmentového dekodéru je k dispozici na PolyLearn a napsal ji profesor Bryan Mealy. Využívá BCD vstup poskytovaný down_counter_FSM1 a vydává desetinný ekvivalent na sedmisegmentovém displeji. Když je čítač zapnutý, je platný vstup vysoký. To umožňuje dekodéru zobrazit desetinné číslo na sedmisegmentovém displeji. Když je čítač vypnutý, je platný vstup nízký. Sedmi segmentový displej pak zobrazí pouze čtyři pomlčky.

Krok 5: Diagram stroje konečného stavu (FSM)

Seznam citlivosti pro konečný automat obsahuje player1, player2, reset a hodiny. Výstup FSM je 2bitový balíček player_LED připojený ke dvěma LED diodám na desce Basys3. Stroj konečných stavů ukazuje následující tři stavy:

ST0 je počáteční stav. V tomto stavu jsou dvě LED diody vypnuté. FSM zůstane v tomto stavu, pokud jsou player1 i player2 na nízké úrovni. Asynchronní reset také nastaví stav na ST0. Když je přepínač player1 nastaven na maximum, další stav bude ST1. Pokud je přepínač player2 nastaven na vysokou hodnotu, bude dalším stavem ST2.

ST1 je stav, pro který svítí LED hráče1. FSM zůstane v tomto stavu pro jakýkoli vstup. To znamená, že i když je přepínač player2 nastaven na vysokou hodnotu bezprostředně poté, co je přepínač player1 vysoký, zůstane v ST1. Pouze asynchronní reset může nastavit další stav na ST0.

ST2 je stav, pro který svítí LED hráče2. Podobně jako ST! FSM zůstane v tomto stavu pro jakýkoli vstup, i když je přepínač player1 nastaven na vysokou hodnotu bezprostředně poté, co je přepínač player2 vysoký. Opět pouze asynchronní reset může nastavit další stav na ST0.

Doporučuje:

Ultratenký domácí automatizační systém WiFi: 6 kroků (s obrázky)

Ultratenký domácí WiFi automatizační systém: V tomto projektu ukážeme, jak můžete v několika krocích vybudovat základní místní domácí automatizační systém. Použijeme Raspberry Pi, které bude fungovat jako centrální WiFi zařízení. Zatímco pro koncové uzly použijeme IOT Cricket k výrobě baterie

Systém třídění barev: Systém založený na Arduinu se dvěma pásy: 8 kroků

Systém třídění barev: Systém založený na Arduinu se dvěma pásy: Přeprava a/nebo balení produktů a položek v průmyslové oblasti se provádí pomocí linek vyrobených pomocí dopravníkových pásů. Tyto pásy pomáhají přesouvat předmět z jednoho bodu do druhého určitou rychlostí. Některé úlohy zpracování nebo identifikace mohou být

Internetový zabezpečovací systém DSC Home Security System: 22 kroků

Internet povolen DSC Home Security System: Upravte stávající systém DSC Home Security tak, aby umožňoval internet a byl monitorován sám. Tento návod předpokládá, že máte fungující Raspberry Pi. Upozorňujeme, že tato implementace má následující nedostatky: Pokud zloděj přeruší přicházející kabel DSL

Konkurenční hra pro 2 hráče VS: 4 kroky

Konkurenční hra pro 2 hráče VS proti načasování: Budete potřebovat: 1. Digital Basys 3, FPGA Board (nebo jakýkoli jiný FPGA,) 2. Relativně aktuální verze Vivado nebo jiného prostředí VHDL3. Počítač, na kterém je možné spustit zmíněný program

Jak správně připojit a nastavit mini HiFi policový systém (zvukový systém): 8 kroků (s obrázky)

Jak správně připojit a nastavit mini HiFi policový systém (zvukový systém): Jsem člověk, kterého baví učit se o elektrotechnice. Jsem střední škola na Ann Richards School for Young Women Leaders. Dělám tento návod, abych pomohl každému, kdo si chce užít svou hudbu z Mini LG HiFi Shelf Syste