Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:19.

- Naposledy změněno 2025-01-23 14:38.

Autor: AmCoderhttps://www.linkedin.com/in/mitu

O: Mitu Raj - Jen Hobbyst a Learner - Chip Designer - Software Developer - Fyzika a nadšenec matematiky Více o AmCoder »

## Toto je nejklikanější a nejpopulárnější odkaz na Googlu pro implementaci VHDL CORDIC ALGORITHM ke generování sinusové a kosinusové vlny ## V současné době existuje mnoho hardwarově efektivních algoritmů, které však nejsou dobře známy kvůli dominanci softwarových systémů nad mnoho let. CORDIC je takový algoritmus, který není ničím jiným než sadou logiky posunu a přidání používané pro výpočet široké škály funkcí včetně určitých goniometrických, hyperbolických, lineárních a logaritmických funkcí. Toto je algoritmus používaný v kalkulačkách atd. Tedy pouhým použitím jednoduchých řadičů a sčítačů můžeme navrhnout hardware s menší složitostí, ale silou DSP pomocí kordického algoritmu. Proto může být navržen jako holý RTL design ve VHDL nebo Verilog bez použití vyhrazených jednotek s plovoucí desetinnou čárkou nebo složitých matematických IP adres.

Krok 1: VHDL a Modelsim

Zde je kordický algoritmus implementován pomocí VHDL pro generování sinusové a cose vlny. Může s vysokou přesností vytvářet sinus a kosinus vstupního úhlu. Kód je syntetizovatelný na FPGA. Modelsim se používá k simulaci návrhu a zkušebního stavu.

Krok 2: Kód VHDL pro návrh a testovací lavici

K reprezentaci čísel s plovoucí desetinnou čárkou se používá technika binárního škálování.

Před kódováním si prosím projděte přiložené dokumenty.

Go thruSimulation cordic_v4.vhd - The Design -The input is angle in 32 bits + sign bit; dokáže zpracovat jakýkoli úhel od 0 do +/- 360 stupňů s přesností vstupu 0,000000000233 stupně. Při zadávání vstupu -> MSB je znaménkový bit a zbytek 32 bitů představuje velikost. -Výstupem návrhu je jeho hodnota sinus a cos v 16 bitech + znaménkový bit.ie; s přesností 0,00001526. Upozorňujeme, že výstup je zobrazen ve formě komplimentu 2, pokud je příslušná hodnota sinus nebo cos záporná. Simulace testb.vhd - testovací lavice pro návrh (1) Vstupní úhly a reset tahu = '0'. Po dvou krocích simulace vytáhněte reset na '1' a "spusťte vše". (2) V okně simulace nastavte radix signálů sin a cos jako desetinný a formát> Analogový (automatický). (3) Oddálením zobrazíte průběh správně.

Krok 3: Připojené soubory

(1) cordic_v4.vhd - Design. (2) testb.vhd - Testovací lavice pro návrh.

(3) Dokument o tom, jak vynutit vstupy úhlu a převést binární výsledky.

Aktualizace: TYTO SOUBORY JSOU ZÁVĚSNÉ A NEJSOU POSKYTOVÁNY. POUŽÍVEJTE PROSÍM SOUBORY Z DALŠÍHO KROKU

Krok 4: Mini -Cordic IP Core - 16 bitů

Omezení výše uvedené implementace je pomalé, nižší hodinová frekvence provozu kvůli provádění výpočtů v jediném hodinovém cyklu. Mini-Cordic IP Core- 16 bitů

- Kritické cesty distribuované do více cyklů za účelem zlepšení výkonu.- Rychlejší- FPGA osvědčený design syntetizovaný až na 100 Mhz hodin.- Více oblasti optimalizované v HDL, menší hardware.- Přidány signály stavu načítání a dokončení.- Pouze nevýhodou je menší rozlišení ve srovnání s předchozí. Testbench:

plně automatizované vstupy s úhlem 0 až 360 stupňů

Připojené soubory: 1) mini cordic main vhdl file2) mini cordic test bench3) Mini Cordic IP Core manual4) Doc o how to force angles and convert results

V případě jakýchkoli dotazů mě neváhejte kontaktovat:

Mitu Raj

sledujte mě:

mail: iammituraj@gmail.com

### Celkový počet stažení: 325 do 01-05-2021 ###

### Poslední úprava kódu: červenec-07-2020 ###

Doporučuje:

Robot s vlastním vyvažováním - Algoritmus řízení PID: 3 kroky

Self Balancing Robot - PID Control Algorithm: Tento projekt byl koncipován, protože jsem měl zájem dozvědět se více o Control Algorithms a jak efektivně implementovat funkční PID smyčky. Projekt je stále ve fázi vývoje, protože ještě bude přidán modul Bluetooth, který bude

Inteligentní popelnice využívající Arduino, ultrazvukový senzor a servomotor: 3 kroky

Inteligentní popelnice využívající Arduino, ultrazvukový senzor a servomotor: V tomto projektu vám ukážu Jak si vyrobit inteligentní popelnici pomocí Arduina, kde se víko popelnice automaticky otevře, když se přiblížíte s odpadky. Dalšími důležitými součástmi použitými k výrobě této inteligentní popelnice jsou ultrazvukové senzory HC-04

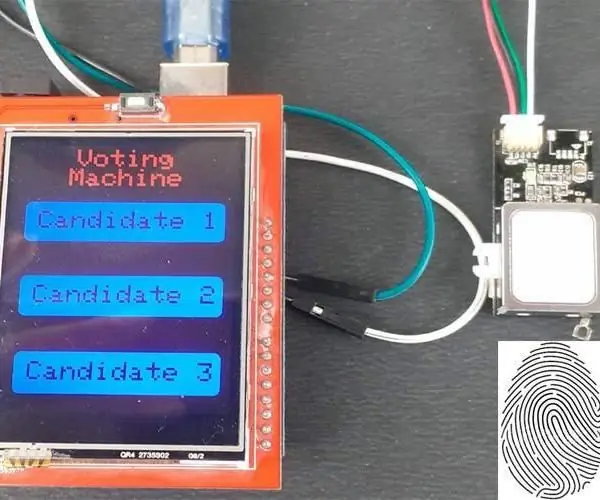

Biometrický hlasovací stroj na bázi otisku prstu využívající Arduino: 4 kroky (s obrázky)

Biometrický hlasovací stroj na bázi otisku prstu využívající Arduino: Všichni víme o stávajícím elektronickém hlasovacím zařízení, kde musí uživatel stisknout tlačítko pro odevzdání hlasu. Ale tyto stroje byly od počátku kritizovány pro temperování. Vláda tedy plánuje zavést základnu otisků prstů

Samovyvažovací robot využívající algoritmus PID (STM MC): 9 kroků

Self Balancing Robot using PID Algorithm (STM MC): V poslední době bylo provedeno mnoho práce na vlastním vyvažování objektů. Koncept vlastního vyvažování začal vyvažováním obráceného kyvadla. Tento koncept se rozšířil i na konstrukci letadel. V tomto projektu jsme navrhli malý mod

Tic Tac Toe na Arduinu s AI (algoritmus Minimax): 3 kroky

Tic Tac Toe na Arduinu s AI (Minimax Algorithm): V tomto Instructable vám ukážu, jak vytvořit hru Tic Tac Toe s AI pomocí Arduina. Můžete buď hrát proti Arduinu, nebo sledovat, jak Arduino hraje proti sobě. Používám algoritmus nazvaný „algoritmus minimax“