Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:18.

- Naposledy změněno 2025-01-23 14:38.

JDM je populární programátor PIC, protože používá sériový port, minimum komponent a nevyžaduje žádné napájení. Ale tam je zmatek tam, s mnoha programátorskými variacemi na internetu, které fungují s kterými PIC? V tomto „pokynu“jsme testovali JDM a já předvádím, jak simulovat obvod pomocí Spice, který zodpoví všechny vaše otázky!

Zásoby

LTspice, který lze stáhnout z Analog Devices zde.

Zde také potřebujete soubory obvodu JDM.

Krok 1: Požadavky na sériový port

JDM vyžaduje sériový port splňující specifikaci EIA232, ideálně s napětím +12/-12.

Podle datového listu Texas Instruments Line Driver MC1488 (obrázek 3)

Výstupní impedance = 4V/8mA = 500 ohmů.

Limit zkratového proudu = 12 mV, bez časového omezení - žádné poškození čipu.

Vstupní impedance linkového přijímače = doporučeno 3k až 7k ohm.

Sériové porty na starších stolních počítačích používají +12v/-12V, které splňují tento požadavek.

Sériové porty na novějších přenosných počítačích používají nižší napětí. JDM může, ale nemusí fungovat - odpověď je složitější.

Krok 2: Požadavky na programování PIC

Informace týkající se požadavků na programování PIC jsou získány od společnosti Microchip. Výše uvedené platí pro typické zařízení.

Krok 3: Specifikace JDM

Ztratily se původní webové stránky JDM v mlze času? Necháme se hádat, co designér původně zamýšlel pro specifikaci.

- Zajistěte VDD = 5V a maximálně IDD = 2mA (pro verzi „v zásuvce“)

- Zajistěte VHH = 13V a maximálně IHH = 0,2mA.

- MCLR Doba náběhu tVHHR = max. 1uS.

- Verze ICSP musí být schopna vytáhnout MCLR low proti 22k pull-up na cíl.

Krok 4: Popis obvodu

Obrázek JDM1 je založen na „standardním“obvodu JDM převzatém z webových stránek PICPgm. Toto je programátor „PIC in Socket“, kde PIC odebírá energii z pinů TX a RTS. Původní diagram byl obtížně srozumitelný, proto jsem jej překreslil pomocí běžné konvence toku proudu shora dolů. A přidal jsem LED indikátory „RESET“, „PROG“a „RTS“, které jsou nutné při konstrukci a testování. Naštěstí to nemá žádný škodlivý vliv na chování.

Normální konvence návrhu obvodu je společná všem zemím, ale klíčovou vlastností JDM je, že uzemnění sériového portu (GND) je připojeno k VDD. To vytváří zmatek, protože signály sériového portu jsou měřeny s ohledem na GND, signály PIC s ohledem na logické uzemnění (VSS).

Když se TX zvýší, Q1 se chová jako dvě dopředně předpnuté diody. (Kolektor Q1 není reverzně zkreslený jako u normálního tranzistorového provozu). Kolektor Q1 nabíjí C2, který je sevřen na VDD+8V Zenerem (D3). Vysílač Q1 dodává 13V do MCLR pro režim Program/Ověření.

Když TX klesne, kondenzátor C3 se nabije přes D1 a VSS se upne na VDD-5V zenerem (D5). Také TX je upnuto na (VSS-0,6) pomocí D1. Q1 je vypnutý, C1 drží svůj náboj pro další programovací impuls. MCLR je upnut na 0V pomocí D2, takže PIC je nyní Reset.

Když je RTS vysoké, hodiny se vysílají do PGC. Svorka D4 PGC s logikou VDD vysoká. Když je RTS nízká, kondenzátor C3 se nabíjí přes D6 a VSS se upíná na VDD-5V zenerem (D5). D6 upíná PGC na VSS nebo logické 0.

Během programování jsou data odeslaná na DTR čtena na PGD, který PIC konfiguruje jako vstup. Když je DTR vysoké, Q2 funguje jako „sledovač emitoru“a napětí PGD je asi (VDD-0,6) nebo logické 1. Když je DTR nízké, Q2 funguje jako špatný tranzistor (piny emitoru a kolektoru jsou obrácené). Q2 táhne PGD low, které je upnuto D7 na VSS nebo logické 0.

Během ověřování konfiguruje PIC PGD jako výstup pro odesílání dat na sériový port. DTR musí být nastaveno vysoko a data jsou čtena na CTS. Když je výstup PGD vysoký, Q2 je vypnutý, CTS = DTR = +12V. Když je výstup PGD nízký, Q2 je zapnutý. Kolektor Q2 odebírá proud (12V+5V)/(1k+1k5) = 7mA z DTR a táhne CTS nízko do VSS.

Krok 5: Příprava na simulaci

Stáhněte si LT spice, uložte a otevřete zde uvedené soubory obvodů (*.asc). Abychom obvod simulovali, musíme mu dát nějaké vstupy, potom „vystopovat“výstupy. V1, V2 V3 simulují sériový port 12V s výstupní impedancí R11, R12, R13.

- V1 generuje 2 programové impulsy na TX od 0,5 ms do 4,5 ms

- V2 generuje sérii datových impulzů na DTR od 1,5 do 4,5 ms

- V3 generuje sérii hodinových impulzů na RTS od 0,5 do 3,5 ms

Součásti V4, X1, R15 a R16 jsou součástí simulace.

- V4 generuje 2 impulsy od 2,5 do 4,5 ms pro ověření dat.

- Propojka X1 simuluje VÝSTUP na PGD.

- R15, R16 simulují „načítání“PIC na VDD a MCLR.

Krok 6: Úpravy pro ICSP

Obrázek JDM3 ukazuje verzi pro programování „v obvodu“. Úpravy oproti originálu jsou

- Vyměňte zásuvku ZIF za konektor ICSP.

- PIC je nyní napájen napájením do cílového obvodu (V5).

- Odstraňte 5V zener (D5).

- Malý kondenzátor 100 pF (C4) je přesunut vedle PIC v cílovém obvodu.

- LED diody odebírají energii z desky plošných spojů, kde je to možné.

- Na cílovém obvodu jsou vyžadovány vytahovací odpor MCLR (R10) a dioda (D10).

- VAROVÁNÍ. Cílová deska musí mít „plovoucí“zdroj, ideálně baterii.

- Nepřipojujte cílovou zem (VSS) k uzemnění počítače/PC připojením jakýchkoli jiných počítačových portů současně s JDM.

Po simulaci JDM1 se ukázal problém dlouhé doby nabíjení na C2. Po přečtení Fruttenboel se zdá, že C2 a Q1 byly přidány jako modifikace originálu. Nedokážu si představit, co mají C2 a Q1 dělat, kromě vytváření problémů. Takže pro JDM4 se vracíme ke staršímu designu na Fruttenboel, který je jednoduchý a srozumitelný. D1 a D3/LED2 svorka MCLR mezi VSS a VDD+8V. Hodnota R1 je snížena na 3k3, což je dostatečné pro osvětlení LED2 při 12V.

JDM4 je také navržen pro práci se slabšími sériovými porty. Když TX stoupne (+9V), zdroj proudu TX = (9-8)/(1k +3k3) = 0,2 ma, jen tolik, aby vytáhl MCLR vysoko, i když nedostatečně k osvětlení LED2. Když TX klesne (asi -7V), proudový odběr TX = (9-7)/1k = 2mA. LED1 proud = (7-2 pro LED)/(2k7) = 1,8 mA. Sbírací proud MCLR = 7-5,5/3k3 = 0,5 mA.

Tento obvod byl také testován (simulace JDM5), aby se zjistilo, co se děje se sériovými porty minimálně +/- 7V, kde není dostatečné napětí pro udržení VHH = 13V. Účel C1 se nyní stává zřejmým. C1 vytváří krátký +ve boost MCLR, 33us hrot na stoupající hraně TX, dostatečně dlouhý na to, aby PIC vstoupil do režimu programování, možná? Odstraňte však propojku X2 (deaktivujte LED1), protože není dostatečný proud k vytažení nízkého MCLR a rozsvícení LED1 dohromady. Když TX klesne, proudový odběr TX = (7V-5,5V)/(1k+3k3) = 0,3mA, což stačí k vytažení MCLR nízko proti pull-up R10.

Krok 7: Výsledky simulace

Chcete-li zobrazit grafické soubory, je lepší kliknout pravým tlačítkem na níže uvedené odkazy a poté vybrat „Otevřít odkaz na nové kartě“

Simulace 1: stopa MCLR, VSS a RTS pro původní JDM1. Okamžitě je zřejmé pozorování 1, 2 a 3.

Simulation 2: trace of MCLR and VSS, and RTS for modified JDM2, which fixes previous problems.

Simulace 3: trasování PGD, VSS a PGC pro odesílání dat JDM2 v programovém režimu. Pozorování 4 při 3,5 mS.

Simulace 4: trasování PGD, VSS a CTS pro JDM2 v ověřovacím režimu (propojka X1 vložena). OK

Simulace 5: Stopa MCLR, VSS, PGD a PGC pro JDM3. ICSP využívající energii z obvodu řeší mnoho problémů.

Simulation 6: trace of MCLR, VSS, PGD and PGC for JDM4 with +/- 9V serial port. MCLR okamžitě stoupá, plně funkční.

Simulace 7: Stopa MCLR, VSS a TX pro JDM5 s odstraněným +/- 7V sériovým portem a propojkou X2. C1 vytváří kladný nárůst (špice) na stoupající hraně MCLR, téměř dostatečný k tomu, aby posunul MCLR nad TX na 13V.

Krok 8: Závěry

Spice je opravdu dobrý v odhalování „skrytých tajemství“provozu obvodu. Obvod JDM evidentně funguje a je kompatibilní s mnoha PIC čipy, ale následující pozorování odhalují možná omezení/problémy s kompatibilitou/chyby?

- Dlouhá doba náběhu MCLR, zatímco C2 se nabíjí na VPP na první puls TX. Selhání specifikace 3.

- Sériový port nabíjí C2, když TX stoupne a RTS klesne. Ale RTS má také za úkol nabíjet C3. Pokud se oba vyskytují současně, vytváří to větší zátěž pro RTS, v důsledku toho C3 ztrácí náboj (VSS stoupá) po 2 ms při simulaci. Selhání specifikace 1.

- C3 se vybije (VSS začne stoupat) poté, co se hodinové impulsy zastaví na 3,5 ms.

- Jaký je účel C2, je vůbec potřeba?

Řešení

- PICPgm pravděpodobně používá softwarové „pracovní kolo“. Musí použít dlouhý TX impuls k přednabíjení na C2, poté vstoupit do programovacího režimu až po druhém TX pulsu? Pro simulaci jsem snížil hodnotu C2 na 1 uF, aby poskytl dobu náběhu 1 ms. Není to ideální řešení.

- Rozdělte C2 a C3 tak, aby se nabíjely nezávisle. Jedna malá modifikace JDM2, C2 je odkazována na GND místo VSS.

- Vyřešeno JDM3. ICSP je mnohem spolehlivější, protože PIC je napájen cílovým obvodem.

- JDM4 řeší problém 1. Jedná se o jednoduchý design, který zcela eliminuje C2.

Krok 9: A nakonec

Důkaz pudinku je v jídle. Tento JDM funguje, takže jej používejte i nadále.

A moje doporučení jsou:

- použijte JDM2 pro programování soketů a 12V sériové porty,

- použijte JDM4 pro programátor ICSP a sériové porty nad +/- 9V,

- použijte JDM4 s odstraněnou propojkou X2 pro sériové porty nad +/- 7V.

Reference:

Koření Analog Devices LT

picpgm

Fruttenboel

Sledujte další projekty PIC na sly-corner

Doporučuje:

Elegoo Super Started Kit Uno R3 Recenze: 4 kroky

Elegoo Super Started Kit Uno R3 Recenze: Před pár dny mi Elegoo poslal na testování tuto Super Starter Kit. Pojďme se tedy podívat, co je uvnitř. Při otevírání tohoto kompaktního pouzdra vidíme spoustu věcí. Na obálce je rejstřík se všemi součástmi. Uvnitř máme kartu s poděkováním se všemi

Počitadlo kroků - mikro: bit: 12 kroků (s obrázky)

Počitadlo kroků - Micro: Bit: Tento projekt bude počítadlem kroků. K měření našich kroků použijeme snímač akcelerometru, který je zabudovaný v Micro: Bit. Pokaždé, když se Micro: Bit zatřese, přidáme 2 k počtu a zobrazíme ho na obrazovce

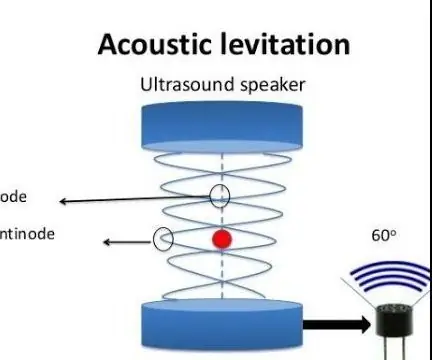

Akustická levitace s Arduino Uno krok za krokem (8 kroků): 8 kroků

Akustická levitace s Arduino Uno krok za krokem (8 kroků): Ultrazvukové měniče zvuku L298N Dc samice napájecí zdroj s mužským DC pinem Arduino UNOBreadboard Jak to funguje: Nejprve nahrajete kód do Arduino Uno (je to mikrokontrolér vybavený digitálním a analogové porty pro převod kódu (C ++)

Bolt - Noční hodiny bezdrátového nabíjení DIY (6 kroků): 6 kroků (s obrázky)

Bolt - Noční hodiny bezdrátového nabíjení DIY (6 kroků): Indukční nabíjení (známé také jako bezdrátové nabíjení nebo bezdrátové nabíjení) je druh bezdrátového přenosu energie. Využívá elektromagnetickou indukci k poskytování elektřiny přenosným zařízením. Nejběžnější aplikací je bezdrátové nabíjení Qi

Jak rozebrat počítač pomocí jednoduchých kroků a obrázků: 13 kroků (s obrázky)

Jak rozebrat počítač pomocí jednoduchých kroků a obrázků: Toto je návod, jak rozebrat počítač. Většina základních komponent je modulární a lze je snadno odstranit. Je však důležité, abyste o tom byli organizovaní. To vám pomůže zabránit ztrátě součástí a také při opětovné montáži