Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:21.

- Naposledy změněno 2025-01-23 14:38.

Naším cílem v rámci tohoto projektu bylo vytvořit něco, co by komunitám šetřilo energii a finanční zdroje. Pouliční osvětlení aktivované pohybem by udělalo obě tyto věci. V celém národě se plýtvá energií na pouliční osvětlení osvětlující ulice, které jsou prázdné. Náš systém pouličního osvětlení zajišťuje, že světla svítí pouze v případě potřeby, což komunitám ušetří nespočet dolarů. Pomocí pohybových senzorů systém rozsvítí světla, pouze když jsou přítomna auta. Kvůli bezpečnosti chodců jsme také implementovali tlačítko pro potlačení, které rozsvítí všechna světla na ulici. Následující kroky vás provedou tím, jak jsme navrhli a postavili náš zmenšený model projektu pomocí Vivado a desky Basys 3.

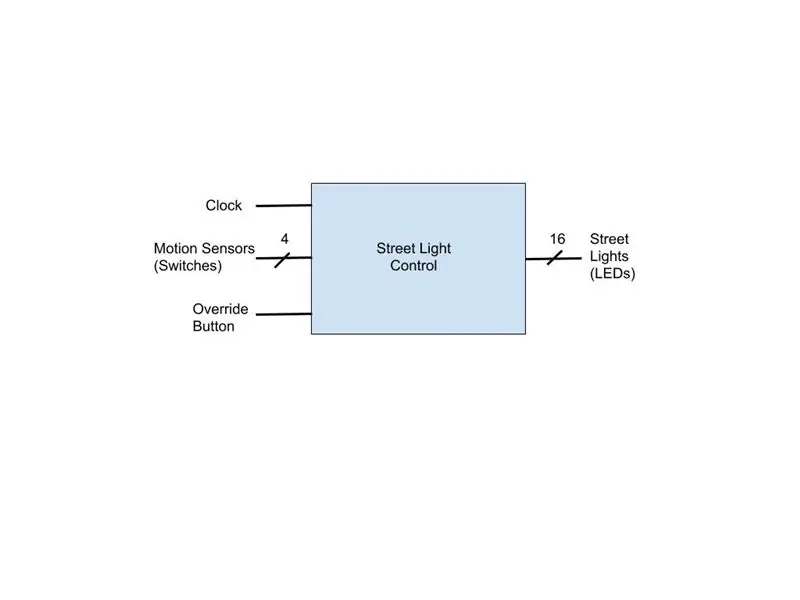

Krok 1: Systémová černá skříňka

Tento projekt jsme zahájili nakreslením jednoduchého diagramu černé skříňky. Schéma černé skříňky jednoduše ukazuje vstupy a výstupy, které náš systém vyžaduje k dokončení všech nezbytných procesů. Snažili jsme se, aby náš design byl co nejjednodušší a nejzákladnější. Naše tři systémové vstupy zahrnovaly sběrnici pohybových senzorů (4 pro náš zmenšený model), tlačítko pro potlačení chodců a hodinový vstup. Na druhé straně je náš jediný výstup sběrnicí LED světel představujících naše pouliční osvětlení. Pro tento model jsme použili scénář 16 pouličních světel jednoduše proto, že to je maximální počet vestavěných LED výstupů na desce Basys 3. Nakonec jsme pomocí tohoto diagramu dokázali vytvořit náš projekt, zdrojové a omezovací soubory Vivado s vhodnými vstupy a výstupy.

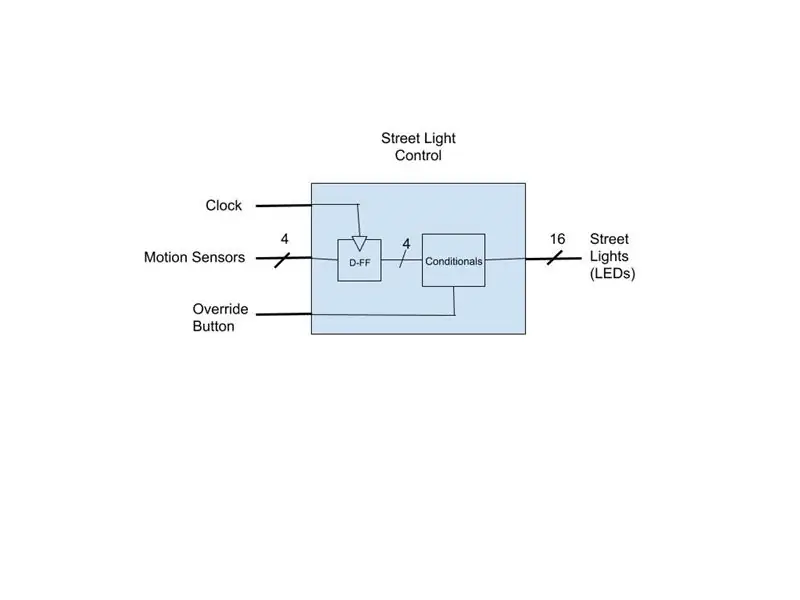

Krok 2: Součásti

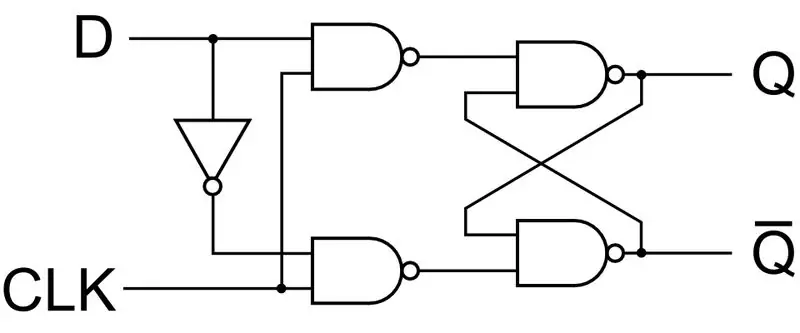

V tomto kroku se ponoříme hlouběji a prozkoumáme součásti, které tvoří náš diagram černé skříňky. Naší první součástí je zdrojový soubor VHDL obsahující D žabky. D klopné obvody jednoduše odebírají jakýkoli signál, který jim vstupuje ze senzorů na stoupající hraně hodin, a zachycují tato data až do další stoupající hrany. Díky tomu naše citlivé snímače pohybu nezpůsobí „blikání“výstupních LED. Také jsme vložili jeden D klopný obvod na vstupní signál tlačítka, aby LED diody svítily asi 5-7 sekund po stisknutí tlačítka. Také jsme to provedli přes dělič hodin.

entita clk_div2 je Port (clk: in std_logic; sclk: out std_logic); konec clk_div2;

architektura my_clk_div z clk_div2 je

konstanta max_count: integer: = (300000000); signál tmp_clk: std_logic: = '0'; begin my_div: process (clk, tmp_clk) proměnná div_cnt: integer: = 0; begin if (rise_edge (clk)) then if (div_cnt = MAX_COUNT) then tmp_clk <= not tmp_clk; div_cnt: = 0; else div_cnt: = div_cnt + 1; konec pokud; konec pokud; sclk <= tmp_clk; ukončit proces my_div; konec my_clk_div;

Naším konečným prvkem v tomto diagramu je behaviorální zdrojový soubor VHDL obsahující podmíněné výstupy na základě konfigurace vstupních signálů.

Krok 3: D Žabky

Čtyři klopné obvody připojené ke vstupním signálům jsou zásadní pro funkčnost našeho systému. Jak již bylo řečeno, u citlivých pohybových senzorů a přepisovacího tlačítka používají klopné obvody pouze výstup našeho vstupního signálu na stoupající hraně hodin. Tato sekvenční logika znamená, že naše pouliční osvětlení může zůstat zapnuto po určitou dobu poté, co bylo spuštěno rychlým pohybem. Kódování D-Flip Flop je velmi jednoduché:

beginprocess (CLK) begin if rise_edge (CLK) then Q <= D; konec pokud; konečný proces;

Celou věc lze zkompilovat do jediného příkazu if. Jakmile jsme měli tento kousek, vytvořili jsme strukturální zdrojový soubor VHDL obsahující všechny čtyři naše potřebné žabky:

begin DFF0: DFF port map (CLK => CLK, D => D (0), Q => Q (0)); DFF1: Mapa portu DFF (CLK => CLK, D => D (1), Q => Q (1)); DFF2: Mapa portu DFF (CLK => CLK, D => D (2), Q => Q (2)); DFF3: Mapa portu DFF (CLK => CLK, D => D (3), Q => Q (3));

konec Behaviorální;

To pomáhá udržovat náš hlavní strukturální soubor, kde spojujeme všechny systémové komponenty mnohem čistěji a organizovaněji.

Krok 4: Podmínky

Aby byl náš kód kompaktní a efektivní, napsali jsme všechny naše podmíněné příkazy do jednoho případu. Pro náš zmenšený model jsme měli 16 možných konfigurací výstupu LED, protože každý pohybový senzor je zodpovědný za skupinu 4 LED diod.:

případ NMS je, když "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; koncový případ;

Krok 5: Omezení

Abyste správně uvedli své vstupy a výstupy pomocí Vivado, musíte implementovat soubor omezení uvádějící všechny používané porty, tlačítka, diody LED a hodiny.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

sada_vlastnosti PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMAGE33 [get_ports U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] PACK_property get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO STANDARDNÍ LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11]} [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTAND {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCM [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

sada_vlastnost PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

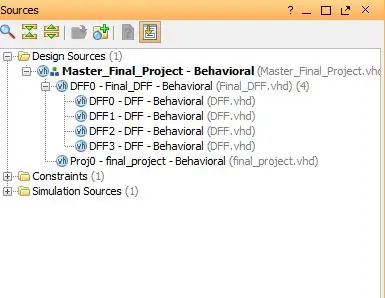

Krok 6: Hlavní zdrojový soubor

V tomto hlavním souboru sdružujeme všechny dříve zmíněné zdrojové soubory komponent. Tento soubor funguje jako strukturální kód spojující nesourodé komponenty.

entita Master_Final_Project je Port (BTN: v STD_LOGIC; CLK: v STD_LOGIC; MS: v STD_LOGIC_VECTOR (3 dolů až 0); LED: out STD_LOGIC_VECTOR (15 až 0)); konec Master_Final_Project;

architektura Behavioral of Master_Final_Project is

komponenta final_project je Port (--CLK: v STD_LOGIC; NMS: v STD_LOGIC_VECTOR (3 dolů až 0); BTN: v STD_LOGIC; --sw: v STD_LOGIC_Vector (1 až 0); LED: mimo STD_LOGIC_VECTOR (15 až 0)); koncová složka;

komponenta Final_DFF je

Port (CLK: ve STD_LOGIC; D: ve STD_LOGIC_Vector (3 dolů až 0); Q: out STD_LOGIC_Vector (3 dolů až 0)); koncová složka;

signál DFF02proj30: STD_LOGIC;

signál DFF12proj74: STD_LOGIC; signál DFF22proj118: STD_LOGIC; signál DFF32proj1512: STD_LOGIC;

začít

DFF0: Mapa portů Final_DFF (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: mapa portů final_project (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); konec Behaviorální;

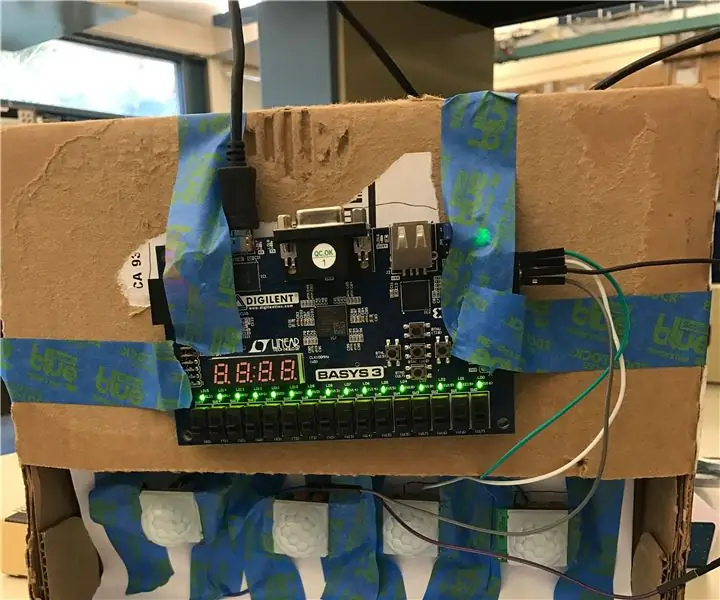

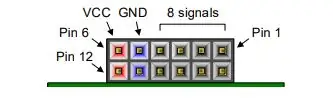

Krok 7: Sestavení

Sestava hardwaru pro tento projekt je minimální. Jediné požadované kusy jsou následující:

1. Základní deska 3 (1)

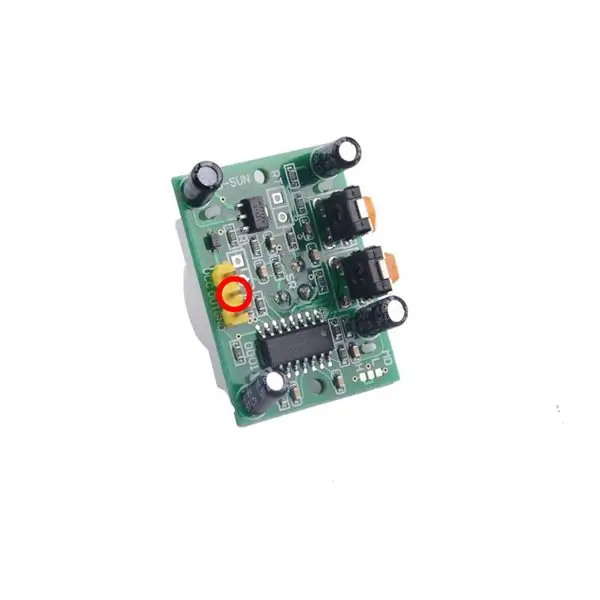

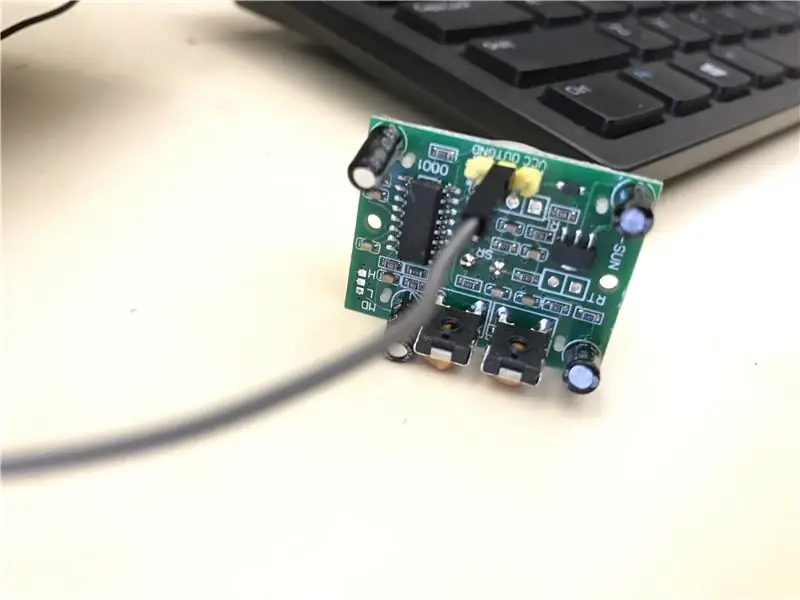

2. Levné pohybové senzory, které najdete na amazonu zde. (4)

3. Vedení muž-žena (4)

Shromáždění:

1. Připojte 4 zástrčky mužského vedení k portům JB záhlaví PMod 1-4 (viz obrázek).

2. Připojte ženské konce k výstupnímu kolíku každého snímače pohybu.

Krok 8: Načtení programu

Nyní jsme připraveni načíst hlavní zdrojový soubor VHDL na desku Basys 3. Ujistěte se, že spustíte syntézu, implementaci a vygenerujete kontrolu bitového proudu pro případné chyby. Pokud jsou všechny spuštěny úspěšně, otevřete správce hardwaru a naprogramujte zařízení Basys 3. Váš projekt je nyní dokončen!

Doporučuje:

Pohybem aktivovaná cosplay křídla využívající obvodové hřiště Express - Část 1: 7 kroků (s obrázky)

Motion Activated Cosplay Wings Using Circuit Playground Express - Část 1: Toto je první část dvoudílného projektu, ve kterém vám ukážu můj postup při výrobě dvojice automatizovaných pohádkových křídel. První částí projektu je mechanika křídel, a druhá část ji dělá nositelnou a přidání křídel

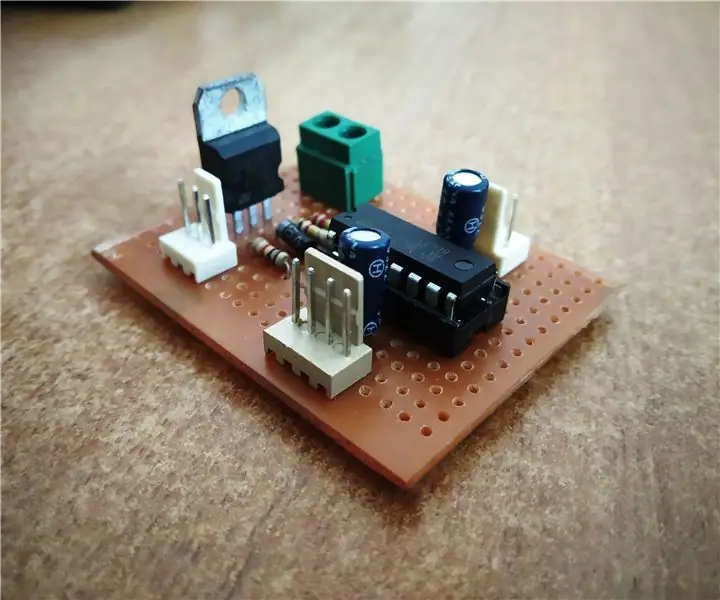

Energeticky účinná deska řidiče motoru: 5 kroků

Energeticky účinná deska ovladače motoru: Předložený projekt je deska s obvody krokového motoru/ovladače motoru s integrovaným obvodem ovladače motoru SN754410 včetně některých funkcí pro úsporu energie. Deska může pohánět 2 stejnosměrné motory nebo krokový motor pomocí duálního H můstkového obvodu v IC. SN754410 IC

Vícekanálový Sonoff - hlasem aktivovaná světla: 4 kroky (s obrázky)

Vícekanálový Sonoff-hlasem aktivovaná světla: před 5 lety se světla v mé kuchyni vydávala cestou do-do. Osvětlení kolejí selhávalo a osvětlení pod pultem bylo jen odpad. Také jsem chtěl rozdělit osvětlení na kanály, abych mohl lépe osvětlit místnost pro rozdíl

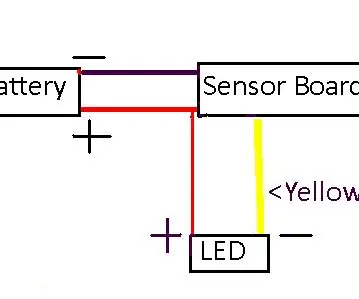

Pohybem aktivovaná LED dioda aktivovaná baterií: 4 kroky

Pohybem aktivovaná LED dioda ovládaná bateriemi: Pokud byste chtěli umístit světlo někam, kde se nedá zapojit, může to být přesně to, co potřebujete

Zásuvka ovládaná pohybem - ze světla snímajícího pohyb: 6 kroků

Zásuvka ovládaná pohybem - ze světla snímajícího pohyb: Představte si, že jste trik nebo ošetřovatel, který jde do toho nejděsivějšího domu v bloku. Poté, co projdete kolem všech démonů, duchů a hřbitovů, se konečně dostanete na poslední cestu. Můžete vidět cukroví v misce před sebou! Ale pak najednou gho