Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:18.

- Naposledy změněno 2025-01-23 14:38.

V tomto tutoriálu použijeme FPGA k ovládání externího LED obvodu. Chystáme se implementovat následující úkoly

(A) K ovládání LED použijte tlačítka na FPGA Cyclone IV DuePrologic.

(B) LED dioda Flash se pravidelně zapíná a vypíná

Video demo

Laboratorní nabídka:

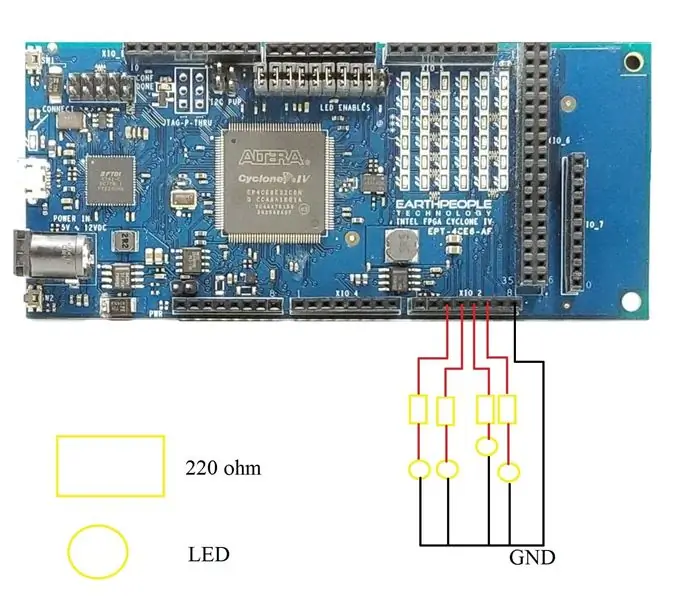

Krok 1: Vybudujte elektronický obvod

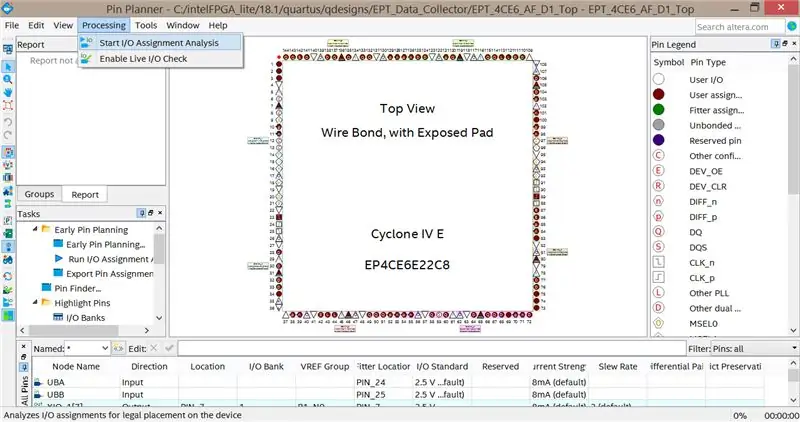

Krok 2: Zkontrolujte Pin Planner a upravte Verilog Code

Krok 3: Upravte kód Verilog

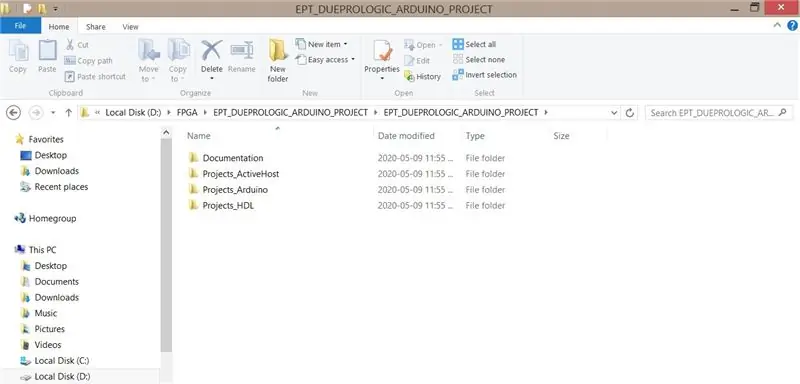

Při nákupu FPGA DueProLogic byste měli obdržet DVD. Po otevření „Projects_HDL“byste měli vidět původní soubor kódu

Přidejte zvýrazněný kód. Zaregistruje I/O porty a přiřadí portům čísla.

výstupní vodič [7: 0] XIO_1, // XIO-D2-D9

výstupní vodič [5: 0] XIO_2, // XIO-D10-D12

výstupní vodič [5: 0] XIO_3, // XIO-D22-D29

vstupní vodič [5: 0] XIO_4, // XIO-D30-D37

vstupní vodič [5: 0] XIO_5, // XIO-D38-D45

výstupní vodič [4: 0] XIO_6_OUT, // XIO-D46-D53

vstupní vodič [31: 5] XIO_6, // XIO-D46-D53

výstupní vodič [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

vstupní vodič UBA, // tlačítkové spínače

vstupní vodič UBB // tlačítkové spínače

přiřadit XIO_1 [3] = start_stop_cntrl;

přiřadit XIO_2 [1] = start_blinky; // LED blesk LED zapíná a vypíná

přiřadit XIO_2 [2] = 1'b1; // výstup VYSOKÝ

přiřadit XIO_2 [3] = ~ UBA; // Stiskněte tlačítko A

přiřadit XIO_2 [4] = UBB; // Stiskněte tlačítko B

přiřadit c_enable = XIO_5 [2];

přiřadit LEDExt = XIO_5 [5];

Poté musíme nastavit časovač zpoždění. Komentujte původní kód časovače a napište novou funkci časovače

//-----------------------------------------------

// LED Blinky start

//-----------------------------------------------

/*

vždy @(posedge CLK_66 nebo negedge RST)

začít

pokud (! RST)

start_blinky <= 1'b0;

jiný

začít

if (control_register [7: 4]> 0)

start_blinky <= 1'b1;

jiný

start_blinky <= 1'b0;

konec

konec

*/

reg [31: 0] ex;

počáteční začátek

ex <= 32'b0;

start_blinky <= 1'b0;

konec

vždy @(posedge CLK_66)

začít

ex <= ex + 1'b1;

pokud (např.> 10 000 000) // zapnutí/vypnutí blesku ~ 1,6 sekundy, hodiny 66 MHz

začít

start_blinky <=! start_blinky;

ex <= 32'b0;

konec

konec

//-----------------------------------------------

// Počítadlo časovače zpoždění LED

//-----------------------------------------------

/*

vždy @(posedge CLK_66 nebo negedge RST)

začít

pokud (! RST)

led_delay_counter <= TIMER_LOW_LIMIT;

jiný

začít

if (state [SELECT_MODE])

led_delay_counter <= hodnota_časovače;

else if (state [WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

konec

konec*/

Krok 4: Kompilace kódu Verilog

V Quartusu stiskněte „Spustit kompilaci“, nemělo by se generovat žádné chybové hlášení.

Pokud se zobrazí chybová zpráva o více pinech. Přejděte na Úkoly -> Zařízení -> Možnosti zařízení a pinů -> Dvojúčelové piny -> změňte hodnotu příslušného pinu na „Použít jako pravidelný I/O“.

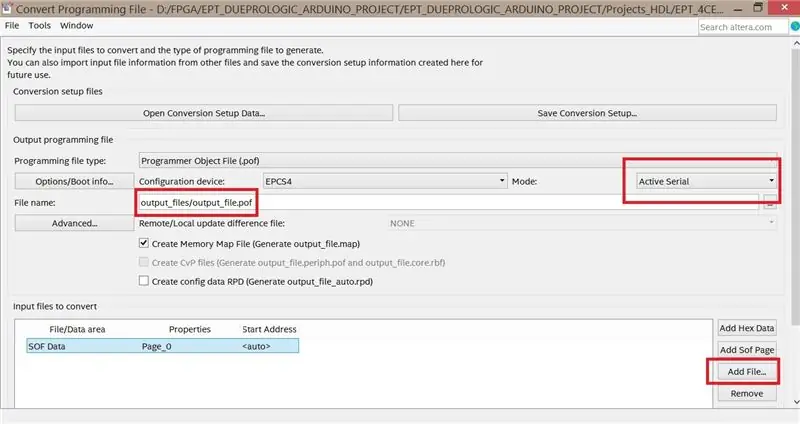

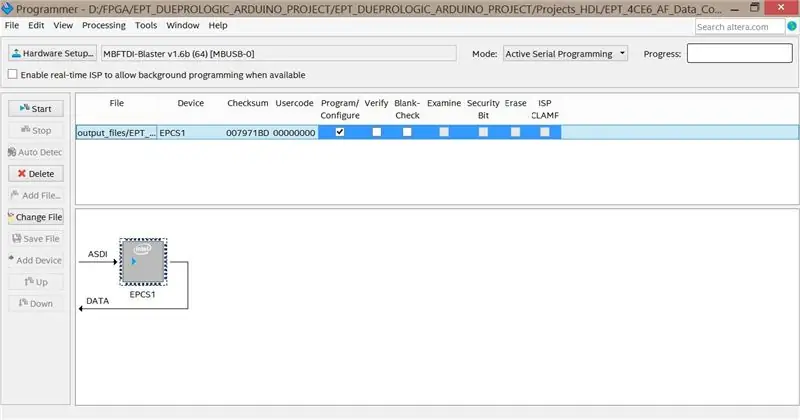

Po kompilaci byste měli získat výstupní soubor pof přímo. Pokud váš software není aktuální, můžete získat pouze soubor sof. Když k tomu dojde, klikněte v Quartusu na „Soubor“-> „převést programovací soubory“. Změňte nastavení, která jsou označena červenými rámečky.

Krok 5: Zkusme to

Přece by to mělo fungovat !!! Žlutá LED dioda vždy svítí. Červená LED bliká. Modrá LED dioda zhasne, když stisknete tlačítko B. Zelená LED se rozsvítí, když stisknete tlačítko A

Doporučuje:

FPGA Cyclone IV DueProLogic ovládá kameru Raspberry Pi: 5 kroků

FPGA Cyclone IV DueProLogic Ovládá kameru Raspberry Pi: Navzdory FPGA je DueProLogic oficiálně navržen pro Arduino, chystáme se komunikovat FPGA a Raspberry Pi 4B. V tomto tutoriálu jsou implementovány tři úkoly: (A) Současně stiskněte dvě tlačítka na FPGA k převrácení úhlu

Servo motor FPGA Cyclone IV DueProLogic ovládá: 4 kroky

Servo motor FPGA Cyclone IV DueProLogic ovládá: V tomto tutoriálu napíšeme kód Verilog pro ovládání servomotoru. Servo SG-90 vyrábí společnost Waveshare. Při koupi servomotoru můžete obdržet katalogový list se seznamem provozního napětí, maximálního točivého momentu a navrhovaného Pu

Arduino Cyclone Game: 5 kroků (s obrázky)

Arduino Cyclone Game: Nikdy jsem nehrál skutečnou cyklónovou arkádovou hru, ale líbí se mi myšlenka hrát s naší reakční dobou. Navrhl jsem miniaturizovanou hru. Skládá se z 32 LED diod tvořících kruh, LED diody se rozsvítí jedna po druhé jako LED chaser. Cílem je stisknout zadek

Cyclone (Arduino LED Game): 6 kroků (s obrázky)

Cyclone (Arduino LED Game): V tomto tutoriálu vás naučím, jak vytvořit LED hru s velmi malým kódem nebo zkušenostmi! Chvíli jsem měl tento nápad a nakonec jsem se dostal k jeho vytvoření. Je to zábavná hra, která nám všem připomíná arkádové hry. Existují další návody

Arkádová hra Arduino Cyclone: 6 kroků

Arkádová hra Arduino Cyclone: Blinky zářivá světla! Arduino! Hra! Co víc je třeba říci? Tato hra vychází z arkádové hry Cyclone, kde se hráč snaží zastavit rolování LED diod kolem kruhu na konkrétním místě