Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:23.

- Naposledy změněno 2025-01-23 14:38.

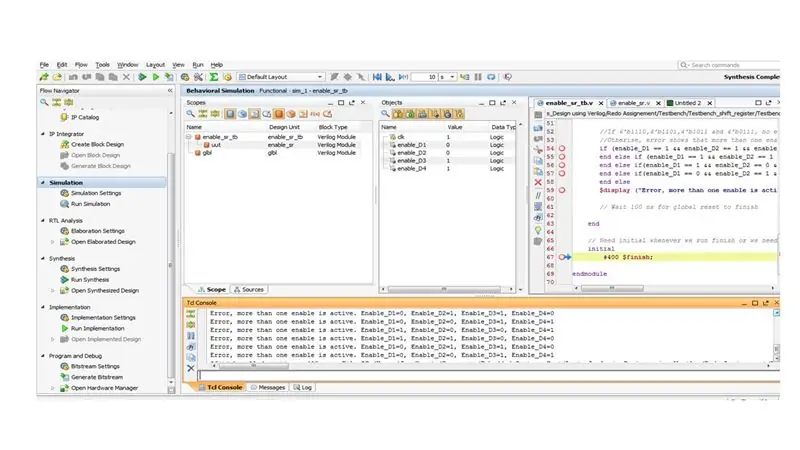

Udělal jsem tento simulační projekt pro online třídu. Autorem projektu je Verilog. Simulaci ve Vivado použijeme k vizualizaci průběhu v enable_sr (povolení číslice) z dříve vytvořeného projektu stopky. Kromě toho použijeme systémovou úlohu k zobrazení chyb, kterých jsme se při návrhu dopustili.

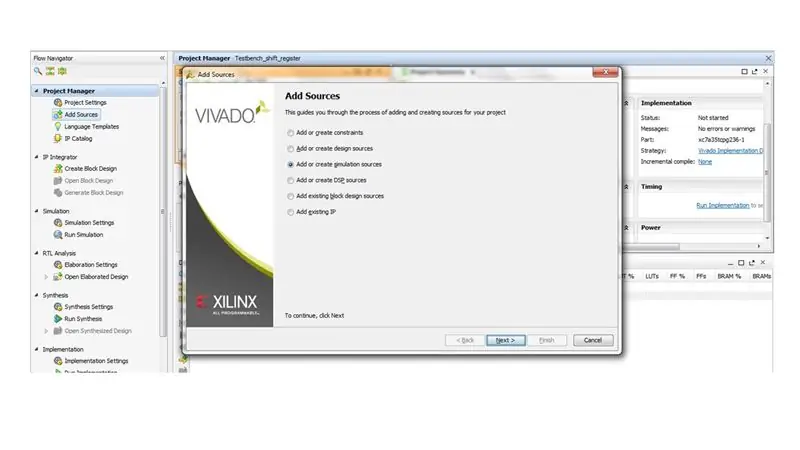

Krok 1: Přidejte zdroje a vyberte „Přidat nebo vytvořit zdroje simulace

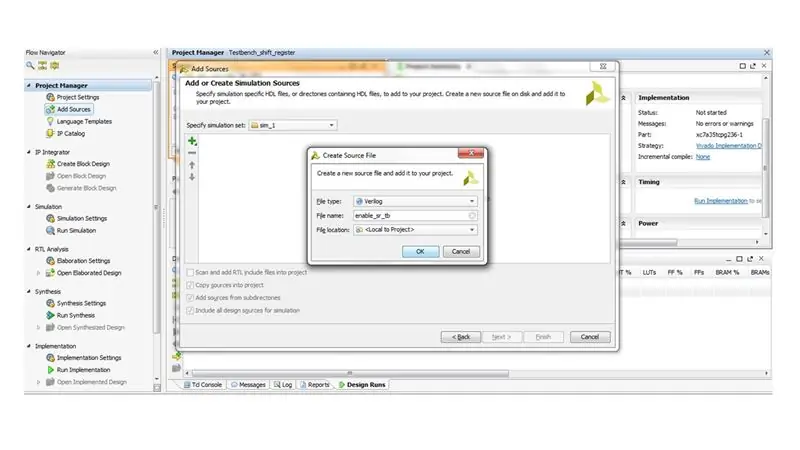

Krok 2: Vytvořte soubor s názvem Enable_sr_tb

Krok 3: Vytvořte soubor Testbench

1. Importujte modul enable_sr z projektu stopky. To je soubor, který chceme simulovat

2. Vytvořte modul testbench enable_sr_tb ();

3. Zadejte vstupy a výstupy modulu enable_sr (). Pamatujte, že vstupy pro enable_sr jsou nyní v typu registru, zatímco výstupy se stanou síťovým typem.

4. Okamžitě testovanou jednotku (uut), což je enable_sr

5. Generujte hodiny, jejichž perioda (T) je 20ns

6. Pomocí podmíněného příkazu vytvořte systém kontroly chyb. V tomto příkladu chceme zkontrolovat, zda je aktivních více než jedna číslice.

Poznámka: V původním souboru enable_sr () bychom měli inicializovat vzor jako 4’b0011, aby byly k vytvoření chyby aktivní dvě číslice

7. Chybu zobrazte pomocí systémové úlohy $ display

8. Pomocí systémové úlohy $ finish dokončete simulaci v čase 400ns

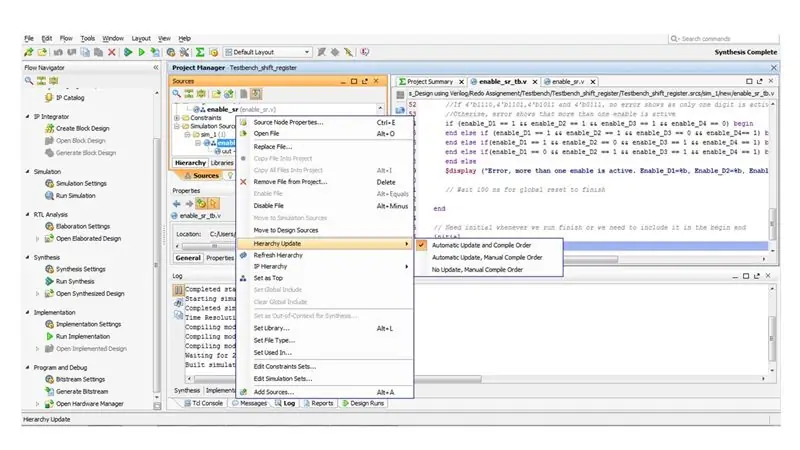

Krok 4: Nastavte Enable_sr_tb jako nejvyšší úroveň v rámci simulace

Krok 5: Spusťte syntézu a simulaci chování

- Před spuštěním simulace chování spusťte syntézu, abyste se ujistili, že v souboru testbench a jednotce v testovacím souboru nejsou žádné chyby syntaxe

- Spusťte simulaci chování

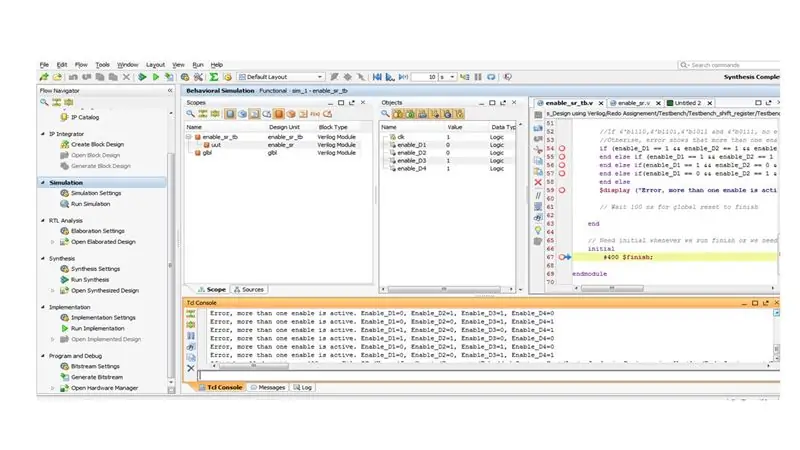

Krok 6: Vyhodnoťte výsledek simulace

Uvidíte okna simulace. Obsahuje různé panely.

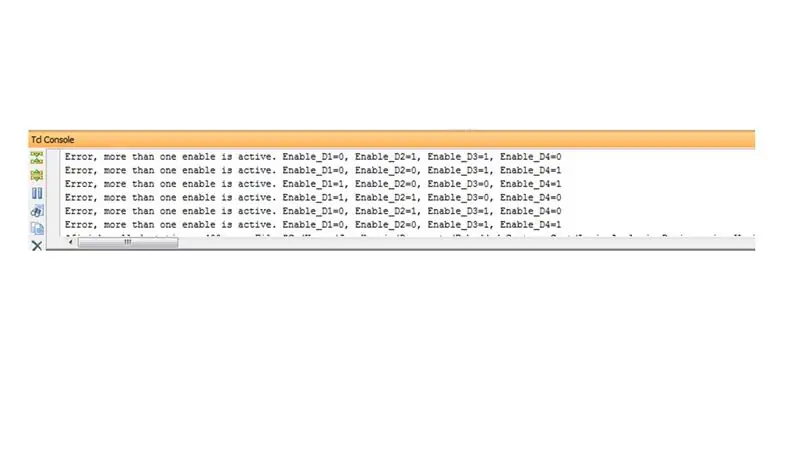

Na panelu konzoly se zobrazí chybová zpráva. To ukazuje, že během období simulace je aktivní více než jedna číslice.

V rozsahu můžete také vidět průběh

V příloze je soubor projektu.

Doporučuje:

Arduino Jak používat 1,3palcový OLED displej SH1106: 7 kroků

Arduino Jak používat 1,3palcový OLED displej SH1106: V tomto tutoriálu se naučíme, jak používat 1,3palcový OLED displej SH1106 Arduino a Visuino software. Podívejte se na video

Jak vytvořit zaváděcí jednotku Linux (a jak ji používat): 10 kroků

Jak vytvořit zaváděcí jednotku Linux (a jak ji používat): Toto je jednoduchý úvod, jak začít s Linuxem, konkrétně Ubuntu

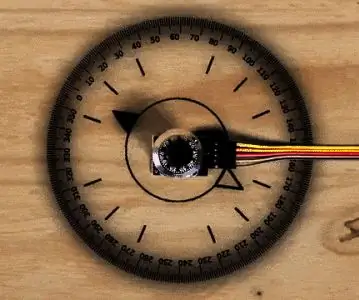

Rotační kodér: Jak funguje a jak jej používat s Arduinem: 7 kroků

Rotační kodér: Jak to funguje a jak používat s Arduinem: Tento a další úžasné návody si můžete přečíst na oficiálním webu ElectroPeak Přehled V tomto tutoriálu se seznámíte s používáním rotačního kodéru. Nejprve uvidíte nějaké informace o rotačním kodéru a poté se naučíte, jak

Jak používat terminál Mac a jak používat klíčové funkce: 4 kroky

Jak používat terminál Mac a jak používat klíčové funkce: Ukážeme vám, jak otevřít terminál MAC. V Terminálu vám také ukážeme několik funkcí, jako je ifconfig, změna adresářů, přístup k souborům a arp. Ifconfig vám umožní zkontrolovat vaši IP adresu a vaši MAC adresu

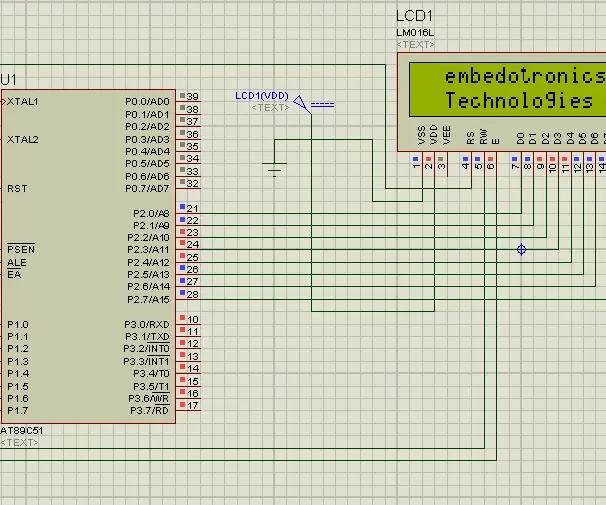

Propojení mikrokontroléru 8051 se 16*2 Lcd v simulaci Proteus: 5 kroků (s obrázky)

Propojení mikrokontroléru 8051 se 16*2 Lcd v simulaci Proteus: Toto je velmi základní projekt 8051. V tomto projektu vám povíme, jak můžeme propojit mikrokontrolér 16*2 lcd s 8051. Zde tedy používáme plný 8bitový režim. V dalším tutoriálu si povíme také o 4bitovém režimu