- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:21.

- Naposledy změněno 2025-01-23 14:38.

Budu analyzovat, jak splňuje náročný návrh napájecího zdroje DC-DC Technologies.

Návrháři energetických systémů čelí neustálému tlaku trhu, aby našli způsoby, jak co nejlépe využít dostupnou energii. U přenosných zařízení vyšší účinnost prodlužuje životnost baterie a přináší větší funkčnost do menších balíčků. Na serverech a základnových stanicích může zvýšení efektivity přímo ušetřit infrastrukturu (chladicí systémy) a provozní náklady (účty za elektřinu). Aby splnili požadavky trhu, návrháři systémů zlepšují procesy přeměny energie ve více oblastech, včetně efektivnější spínací topologie, inovací balení a nových polovodičových zařízení na bázi karbidu křemíku (SiC) a nitridu galia (GaN).

Krok 1: Zlepšení topologie převaděče

Aby lidé plně využili dostupné energie, stále častěji přebírají návrhy založené na spínací technologii, nikoli na lineární technologii. Spínaný napájecí zdroj (SMPS) má efektivní výkon přes 90%. To prodlužuje životnost baterie přenosných systémů, snižuje náklady na elektřinu u velkých zařízení a šetří místo, které se dříve používalo pro součásti chladiče.

Přechod na přepnutou topologii má určité nevýhody a jeho složitější design vyžaduje, aby designéři měli více dovedností. Konstruktéři musí být obeznámeni s analogovými a digitálními technologiemi, elektromagnetikou a řízením v uzavřené smyčce. Návrháři desek plošných spojů (PCB) musí věnovat větší pozornost elektromagnetickému rušení (EMI), protože vysokofrekvenční spínací průběhy mohou způsobovat problémy v citlivých analogových a RF obvodech.

Před vynálezem tranzistoru byl navržen základní koncept převodu spínaného výkonu: například indukční výbojový systém typu Kate vynalezený v roce 1910, který pomocí mechanického vibrátoru implementoval flyback boost konvertor pro automobilový zapalovací systém.

Většina standardních topologií existuje již desítky let, ale to neznamená, že by inženýři neupravovali standardní návrhy tak, aby vyhovovaly novým aplikacím, zejména řídicím smyčkám. Standardní architektura používá pevnou frekvenci k udržení konstantního výstupního napětí přiváděním zpět části výstupního napětí (řízení režimu napětí) nebo ovládáním indukovaného proudu (ovládání režimu proudu) za různých podmínek zatížení. Designéři se neustále zlepšují, aby překonali nedostatky základního designu.

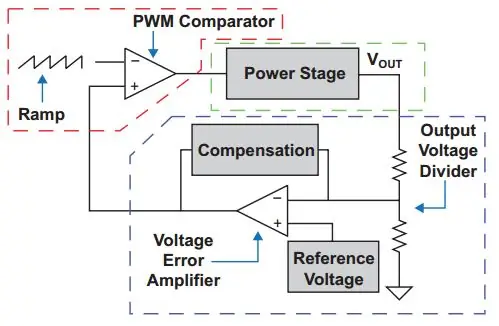

Obrázek 1 je blokové schéma základního systému řízení napětí v uzavřené smyčce (VMC). Výkonový stupeň se skládá z vypínače a výstupního filtru. Kompenzační blok obsahuje dělič výstupního napětí, zesilovač chyb, referenční napětí a komponentu pro kompenzaci smyčky. Modulátor šířky impulzů (PWM) používá komparátor k porovnání chybového signálu se signálem s pevnou rampou k vytvoření sekvence výstupních impulsů, která je úměrná chybovému signálu.

Ačkoli různá zatížení systému VMC mají přísná výstupní pravidla a lze je snadno synchronizovat s externími hodinami, má standardní architektura určité nevýhody. Kompenzace smyčky zmenšuje šířku pásma řídicí smyčky a zpomaluje přechodovou odezvu; zesilovač chyb zvyšuje provozní proud a snižuje účinnost.

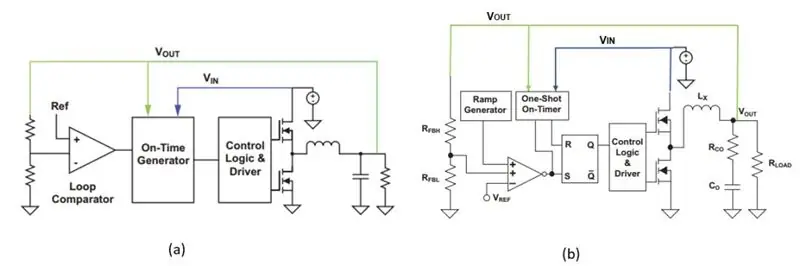

Schéma řízení konstantního zapnutí (COT) poskytuje dobrý přechodový výkon bez kompenzace smyčky. Ovládání COT používá komparátor k porovnání regulovaného výstupního napětí s referenčním napětím: když je výstupní napětí menší než referenční napětí, generuje se pevný časový impuls. Při nízkých pracovních cyklech to způsobuje, že spínací frekvence je velmi vysoká, takže adaptivní regulátor COT generuje čas zapnutí, který se mění se vstupním a výstupním napětím, což udržuje frekvenci v ustáleném stavu téměř konstantní. Topologie D-CAP společnosti Texas Instrument je vylepšení oproti adaptivnímu přístupu COT: řadič D-CAP přidává na vstup komparátoru zpětné vazby napětí rampy, což zlepšuje výkon chvění snížením pásma šumu v aplikaci. Obrázek 2 je srovnání systémů COT a D-CAP.

Obrázek 2: Srovnání standardní topologie COT (a) a topologie D-CAP (b) (Zdroj: Texas Instruments) Existuje několik různých variant topologie D-CAP pro různé potřeby. Například řadič PPS s polovičním můstkem TPS53632 využívá architekturu D-CAP+, která se používá především v aplikacích s vysokým proudem a dokáže řídit úrovně výkonu až 1 MHz v převodnících POL od 48 V do 1 V s účinností až 92%.

Na rozdíl od D-CAP přidává zpětnovazební smyčka D-CAP+ komponentu, která je úměrná indukovanému proudu pro přesné ovládání poklesu. Zesílený zesilovač chyb zlepšuje přesnost stejnosměrného zatížení za různých podmínek linky a zatížení.

Výstupní napětí regulátoru je nastaveno interním DAC. Tento cyklus začíná, když aktuální zpětná vazba dosáhne úrovně chybového napětí. Toto chybové napětí odpovídá zesílenému rozdílu napětí mezi napětím žádané hodnoty DAC a výstupním napětím zpětné vazby.

Krok 2: Zlepšete výkon za podmínek lehkého zatížení

U přenosných a nositelných zařízení je třeba zlepšit výkon při nízkém zatížení, aby se prodloužila životnost baterie. Mnoho přenosných a nositelných aplikací je většinu času v pohotovostním režimu „dočasného spánku“nebo „spánku“s nízkou spotřebou, aktivuje se pouze v reakci na vstup uživatele nebo periodická měření, takže minimalizujte spotřebu energie v pohotovostním režimu. Je to nejvyšší priorita.

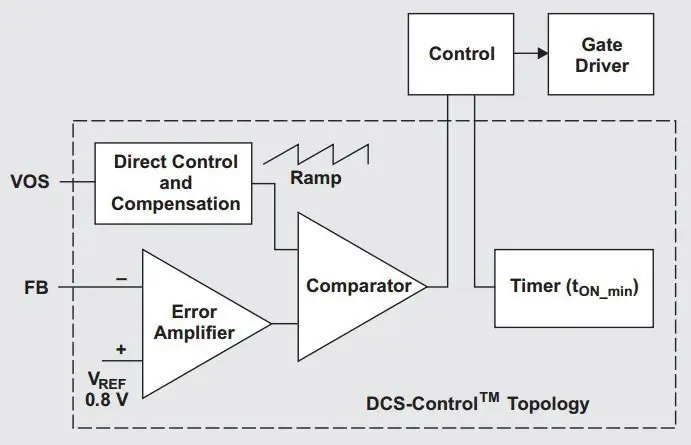

Topologie DCS-ControlTM (Direct Control to Seamless Transition to Energy Saver Mode) kombinuje výhody tří různých schémat ovládání (tj. Režim hystereze, napěťový režim a aktuální režim) pro zlepšení výkonu při světelném zatížení, zejména přechod na opuštění stavu lehkého zatížení. Tato topologie podporuje režimy PWM pro střední a těžké zatížení a také režim úspory energie (PSM) pro lehké zatížení.

Během provozu PWM systém pracuje na své jmenovité spínací frekvenci na základě vstupního napětí a řídí změnu frekvence. Pokud se proud zátěže sníží, převodník se přepne na PSM, aby byla zachována vysoká účinnost, dokud neklesne na velmi nízké zatížení. Při PSM se spínací frekvence lineárně snižuje s proudem zátěže. Oba režimy jsou řízeny jediným řídicím blokem, takže přechod z PWM do PSM je bezproblémový a nemá vliv na výstupní napětí.

Obrázek 3 je blokové schéma DCS-ControlTM. Řídicí smyčka přijímá informace o změně výstupního napětí a přivádí je přímo zpět do rychlého komparátoru. Komparátor nastavuje spínací frekvenci (jako konstantu pro ustálené provozní podmínky) a poskytuje okamžitou reakci na dynamické změny zatížení. Zpětnovazební smyčka napětí přesně reguluje stejnosměrné zatížení. Interně kompenzovaná regulační síť umožňuje rychlý a stabilní provoz s malými externími součástmi a kondenzátory s nízkým ESR.

Obrázek 3: Implementace topologie DCS-ControlTM v převodníku buck TPS62130 (Zdroj: Texas Instruments)

Synchronní měnič výkonu TPS6213xA-Q1 je založen na topologii DCS-ControlTM a je optimalizován pro aplikace POL s vysokou hustotou výkonu. Typická spínací frekvence 2,5 MHz umožňuje použití malých cívek a poskytuje rychlou přechodovou odezvu a vysokou přesnost výstupního napětí. TPS6213 pracuje s rozsahem vstupního napětí 3V až 17V a může dodávat až 3A nepřetržitého proudu mezi výstupním napětím 0,9V a 6V.

Doporučuje:

Obnovení starého napájecího zdroje pro PC: 12 kroků (s obrázky)

Obnova starého napájecího zdroje pro PC: Od devadesátých let 20. století vtrhly do světa počítače. Situace trvá dodnes. Starší počítače, do roku 2014 … 2015, jsou z velké části mimo provoz. Protože každý počítač má napájecí zdroj, velké množství z nich je opuštěno ve formě odpadu

Oddělovací pouzdro napájecího zdroje ATX: 3 kroky

ATX napájecí zdroj Breakout Case: Koupil jsem níže uvedenou rozbíjecí desku ATX a potřeboval jsem k ní pouzdro. Materiály ATX Breakout deska Starý napájecí zdroj ATX Šrouby a matice (x4) 2,5 mm samořezné šrouby Podložky (x4) Kolébkový spínač Kabelové pásky Teplem smrštitelná trubice Pájka 3D vlákno (zadní a zesilovač; žhnoucí

Semi-pasivní chlazení napájecího zdroje počítače: 3 kroky

Semi-pasivní chlazení napájecího zdroje počítače: Dobrý den! Základní myšlenkou je, že pokud jde o napájecí zdroj s velkou výkonovou rezervou, pak není třeba neustále otáčet ventilátor (stejně jako se to dělalo ve ventilátoru CPU). Pokud je tedy spolehlivé sledovat teplotu napájecího zdroje

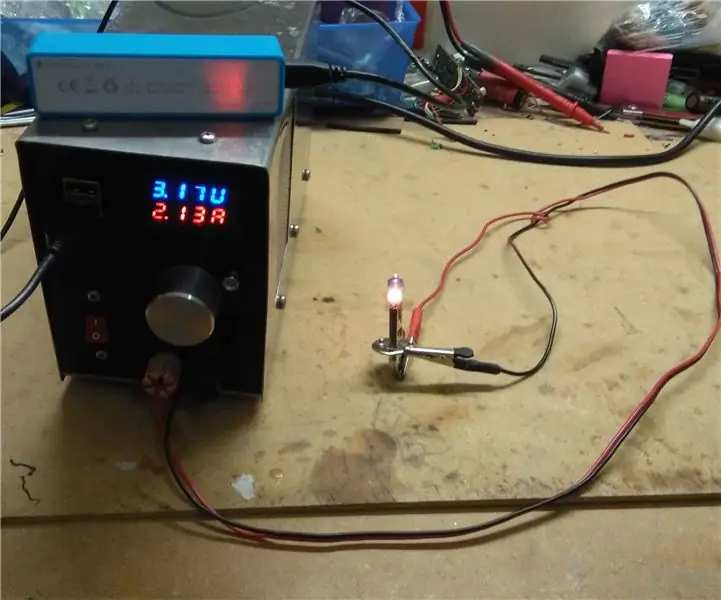

Stavba napájecího zdroje s nastavitelnou lavicí: 4 kroky (s obrázky)

Sestavení napájecího zdroje s nastavitelným stolem: Používám starý napájecí zdroj založený na lineárním regulátoru již mnoho let, ale maximální výkon 15V-3A spojený s nepřesnými analogovými displeji mě přiměl k vytvoření vlastního napájecího zdroje, který řeší tyto problémy. Podíval jsem se na další

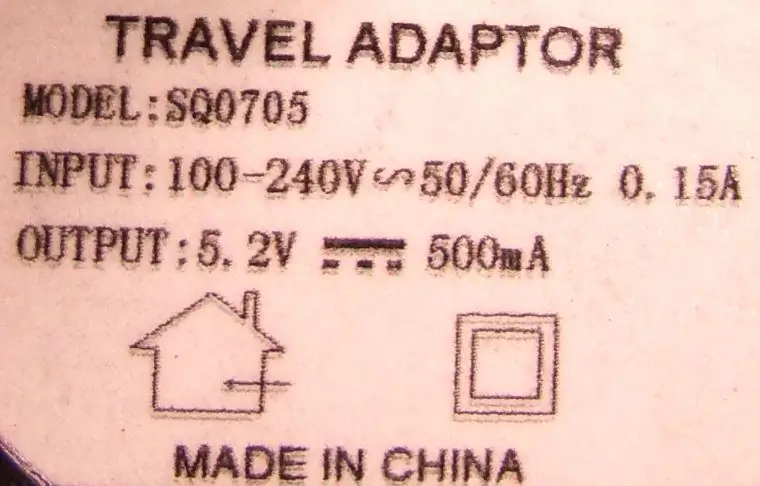

Změna výstupního napětí levného napájecího zdroje: 3 kroky

Změna výstupního napětí levného napájecího zdroje: Tento návod ukazuje, jak vyměnit součásti uvnitř malého napájecího zdroje, aby bylo možné výstupní napětí přizpůsobit vašim potřebám. Pro DIY projekt jsem potřeboval stabilizované napětí přesně 7V dc a asi 100 mA. Když jsem se rozhlédl po své sbírce dílů, našel jsem