Obsah:

- Krok 1: Blokový diagram

- Krok 2: Princip činnosti

- Krok 3: Implementace logiky

- Krok 4: Vyřešení zablokování

- Krok 5: Konfigurace zařízení - obvod Matrix0

- Krok 6: Konfigurace zařízení - logika hodin SPI

- Krok 7: Konfigurace zařízení - vlastnosti komponent Matrix0

- Krok 8: Konfigurace zařízení - obvod Matrix1

- Krok 9: Konfigurace zařízení - 3bitový binární čítač

- Krok 10: Konfigurace zařízení - 3bitová porovnávací logika

- Krok 11: Konfigurace zařízení - digitální porovnávací logika a dočasný registr

- Krok 12: Konfigurace zařízení - vlastnosti komponent Matrix1

- Krok 13: Výsledky

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:20.

- Naposledy změněno 2025-01-23 14:38.

Řídicí systémy a související zařízení pracují s více zdroji energie, jako jsou napěťové linky nebo baterie, a musí sledovat nejvyšší (nebo nejnižší) linku mezi danou sadou.

Například přepínání zátěže v systému napájeném „více bateriemi“vyžaduje, aby systém monitoroval buď minimální nebo maximální napětí mezi polem baterií (max. Nebo min. Jako funkce konkrétního spínacího algoritmu) a dynamicky směroval zátěž do nejvhodnější zdroj v reálném čase. Alternativně může systém kvůli správnému nabíjení dočasně odpojit baterii nejnižšího napětí.

Dalším příkladem je moderní solární systém, kde je každý solární panel vybaven mechanismem tiltrotátu a solárním sledovacím obvodem (druhý poskytuje informace o poloze Slunce pro orientaci panelu). S informacemi o maximálním napětí lze každou polohu solárního panelu doladit na základě toho, že panel strun skutečně dodává nejvyšší výstupní napětí, čímž se dosáhne vynikající úrovně optimalizace výkonu.

Existuje několik různých značek komerčních integrovaných obvodů (hlavně mikrokontroléry), které mohou v zásadě implementovat sledovač maximálního napětí. Vyžadují však programování a jsou méně nákladově efektivní než řešení se smíšeným signálem. Doplnění designu Dialog GreenPAKTM může pozitivně ovlivnit cenovou dostupnost, velikost a modularitu designu. Tento design využívá výhod integrace analogových i digitálních obvodů do jednoho čipu.

V tomto Instructable je implementován analogový front-end a digitální logika potřebná k implementaci vyhledávače napětí max. (Nebo případně min.) Mezi osm různých zdrojů.

K implementaci 8kanálového analogového monitoru napětí max/min se používá SLG46620G.

Níže jsme popsali potřebné kroky, abychom pochopili, jak bylo řešení naprogramováno pro vytvoření 8kanálového analogového monitoru napětí max/min. Pokud však chcete získat pouze výsledek programování, stáhněte si software GreenPAK a zobrazte již dokončený soubor návrhu GreenPAK. Připojte vývojovou sadu GreenPAK k počítači a spusťte program a vytvořte 8kanálový analogový monitor napětí max/min.

Krok 1: Blokový diagram

Obrázek 1 ukazuje globální diagram implementovaného systému.

Řetězec až 8 zdrojů proměnného napětí je multiplexován a propojen s ADC modulem GreenPAK připojeným k přizpůsobenému internímu designu, který je schopen vybrat zdroj s nejvyšším napětím vzhledem k ostatním. Interní logika vydává tyto informace pro zobrazení nebo další zpracování.

Design je založen na produktu GreenPAK SLG46620G, protože obsahuje všechny potřebné analogové a digitální stavební bloky pro aplikaci. V této implementaci je pole skenováno pomocí analogového multiplexeru ADG508 přímo poháněného integrovaným obvodem GreenPAK.

Výstupní informací je 3bitové digitální číslo odpovídající číslu zdroje napětí při maximálním napětí. Přímý způsob, jak získat tyto informace, je zobrazit číslo pomocí 7segmentového displeje. Toho lze snadno dosáhnout propojením digitálního výstupu SLG46620G se 7segmentovým ovladačem displeje, jako je řešení GreenPAK popsané v Referenci nebo se společným 74LS47 IC.

Předložený obvod hledá maximální napětí. Chcete-li převést konstrukci na vyhledávač minimálního napětí, musí být mezi analogový multiplexor a analogový vstup GreenPAK přidán jednoduchý obvod předběžné úpravy, který odečte výstup multiplexeru od referenčního napětí 1 V.

Krok 2: Princip činnosti

Cílem návrhu je vybrat zdroj s maximálním napětím, proto se skenování provede na celém poli, přičemž se uloží poslední maximální hodnota a porovná se s další hodnotou na vstupu (která patří k dalšímu zdroji napětí ve skenování).

V následujícím textu budeme odkazovat na kompletní multiplexní sekvenci podél všech vstupů jako „skenování“nebo „smyčka“.

Porovnání mezi dvěma hodnotami není provedeno pomocí komponent ACMP (je však k dispozici v SLG46620G), ale spíše pomocí modulu DCMP, jakmile jsou hodnoty příslušně digitalizovány. Jedná se o pokročilou a zdokonalenou techniku, kterou jsme poprvé řešili v Reference.

Obrázek 2 ukazuje, jak je SLG46620G strukturován pro tento design.

Analogový vstupní signál jde na vstup ADC přes komponentu PGA s nastaveným ziskem 1. Je také možné různé nastavení zisku, aby bylo možné najít nejlepší shodu s přední elektronikou pro úpravu určenou pro mapování vstupního napětí na 0-1 V rozsah modulu GreenPAK ADC.

ADC pracuje v režimu s jedním koncem a převádí analogový signál na 8bitový digitální kód, který je poté přenesen do modulu DCMP. Digitální kód je také přiveden do bloku SPI, nakonfigurovaného jako ADC/FSM Buffer, kde lze uložit digitální kód a nezmění se, dokud na vstup SPI CLK nepřijde další impuls. Všimněte si, že vyhrazený logický blok pohání vstup SPI CLK. Tuto část prozkoumáme později, protože toto je „základní“logika zodpovědná za správnou funkci. Nový digitální kód je uložen do modulu SPI pouze tehdy, pokud patří skutečnému maximálnímu vstupnímu napětí.

Komponenta DCMP se používá k porovnání aktuálních dat ADC s posledním vítězem (to je poslední nalezené maximum), který je uložen v bloku SPI. Generuje impuls na výstupu OUT+, když jsou nová data ADC větší než ta předchozí. Signál OUT+ používáme k aktualizaci bloku SPI s novým vítězem.

Globální hodinový signál pohání převody ADC a obecné časování. Jakmile je konverze provedena, pulzuje výstupní signál ADT ADC, koordinovaný v čase s paralelním výstupem dat ADC. Výstup INT používáme také ke zvýšení 3bitového binárního čítače implementovaného DFF v Matrix1, což je užitečné ze tří důvodů:

1. Výstupní linky čítače adresují externí analogový multiplexor, čímž slouží dalšímu vstupnímu napětí do ADC;

2. Počet se zmrazí do 3bitového registru (implementovaného v Matrixu 1), aby se dočasný vítěz během skenování uložil;

3. Počet je dekódován pro aktualizaci druhého 3bitového registru (implementovaného v Matrix0), jakmile je skenování dokončeno.

Krok 3: Implementace logiky

Modul ADC postupně poskytuje převedená data všech vstupních napětí, jedno po druhém, neomezeně dlouho. Jakmile je multiplexer adresován 0b111 (desítkově 7), čítač se odvalí na 0b000 (desetinná 0), čímž zahájí nové skenování vstupních napětí.

Během skenování je výstupní signál ADC INT generován, když je paralelní datový výstup platný. Když tento signál pulzuje, analogový multiplexor se musí přepnout na další vstup a poskytnout PGA odpovídající napětí. Proto je výstup ADC INT přímým taktovacím signálem 3bitového binárního čítače z obrázku 2, jehož 3bitové paralelní výstupní slovo přímo adresuje externí analogový multiplexor („V výběr“na obrázku 1).

Podívejme se nyní na příklad, kde mají mít vstupní napětí následující vztahy:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Obrázek 3 představuje hlavní signály zapojené do mechanismu maximálního rozhodování.

Protože data jsou nakonec taktována do registru vyrovnávací paměti SPI synchronně s impulsy INT, existuje srovnávací okno, kde je obsah vyrovnávací paměti SPI porovnáván s dalším výsledkem převodu ADC. Toto konkrétní načasování má za následek generování impulsů OUT+ na výstupu DCMP. Můžeme využít výhod těchto impulsů k načtení nových hodnot do registru vyrovnávací paměti SPI.

Jak je patrné z datového řádku vyrovnávací paměti SPI na předchozím obrázku, registr SPI vždy obsahuje čas od času největší hodnotu mezi 8 vstupy a aktualizuje se pouze tehdy, když modul DCMP detekuje větší hodnotu (s odkazem na DCMP OUT+ výstupní řádek grafu, chybějící impulsy způsobí, že V2 zůstane v registru zablokováno, dokud nebude porovnáno s V5).

Krok 4: Vyřešení zablokování

Pokud by implementovaná logika byla stejná, jak je popsáno výše, je jasné, že bychom narazili na situaci zablokování: systém je schopen detekovat pouze vyšší napětí, než jaké odpovídá tomu, co je uloženo v registru vyrovnávací paměti SPI.

To platí také v případě, že by se toto napětí snížilo a pak by se další vstup, dosud nižší než ten, stal nejvyšším: nikdy by nebyl detekován. Tato situace je lépe vysvětlena na obrázku 4, kde jsou přítomna pouze 3 vstupní napětí z důvodu jasnost.

V době iterace 2 klesá V3 a V1 je skutečné maximální napětí. Modul DCMP však neposkytuje impuls, protože data uložená do vyrovnávacího registru SPI (odpovídá 0,6 V) jsou větší než data odpovídající V1 (0,4 V).

Systém se pak chová jako „absolutní“maximální vyhledávač a neaktualizuje výstup správně.

Pěkný způsob, jak tento problém vyřešit, je vynutit opětovné načtení dat do registru vyrovnávací paměti SPI, když systém dokončí celý cyklus dotazování všech kanálů.

Ve skutečnosti, pokud je napětí na tomto vstupu stále nejvyšší, nic se nezmění a řízení bezpečně pokračuje (viz obrázek 4 výše, to je případ smyčkových iterací 0 a 1). Na druhou stranu, pokud se napětí na tomto vstupu náhodou sníží na hodnotu menší než jiný vstup, pak opětovné načtení hodnoty dává modulu DCMP možnost generovat impuls OUT+ při porovnávání s novou maximální hodnotou (to je případ opakování smyček 2 a 3).

K překonání problému je nutný kus logického obvodu. Když smyčka dosáhne skutečného maximálního vstupu, musí generovat hodinový signál do součásti SPI, a tak vynutit opětovné načtení aktualizovaného datového slova do registru vyrovnávací paměti SPI. Toto bude projednáno v oddílech 7.2 a 7.6 níže.

Krok 5: Konfigurace zařízení - obvod Matrix0

SLG46620G má dva maticové bloky, jak je znázorněno na obrázku 2. Následující obrázky ukazují příslušné konfigurace zařízení.

Horní část obvodu je „smyčkový registr“realizovaný pomocí 3 DFF (DFF0, DFF1 a DFF2). Po každé smyčce vstupního multiplexeru se obnoví, aby se do 7segmentového ovladače displeje odeslalo binární číslo „vítěz“, tj. Vstup s nejvyšším napětím v posledním skenování. Jak hodiny do DFF, tak data pocházejí z logiky implementované v Matrix1 přes port P12, P13, P14 a P15.

Spodní část je analogová přední část se vstupem na pinu 8 a PGA se ziskem x1. Výstup ADC INT jde jak do logiky taktování SPI, tak do Matrix1 přes port P0, kde bude sloužit jako hodinový signál pro implementovaný čítač.

Paralelní datové výstupy ADC a SPI jsou označeny NET11 a NET15 pro připojení ke komponentě DCMP v Matrix1.

Krok 6: Konfigurace zařízení - logika hodin SPI

Jak bylo zdůrazněno dříve v části „Implementace logiky“, registr vyrovnávací paměti SPI se aktualizuje pokaždé, když srovnání mezi skutečnou uloženou hodnotou a novými daty převodu ADC generuje impuls na výstupu DCMP OUT+.

Integrita signálu je zajištěna, pokud je tento signál AND-ed s výstupem ADC INT. Tím se zabrání jakémukoli špici a falešnému spouštění.

Rovněž jsme zdůraznili, že k přeskočení zablokování je nutné aktualizovat vyrovnávací paměť SPI, když smyčka dosáhne skutečných údajů o vítězi.

Tři signály jsou pak ve hře o správné taktování SPI:

1. Výstup ADC INT (LUT0-IN1)

2. Výstup DCMP OUT+ (LUT0-IN0 přes port P10)

3. Počet odpovídá signálu západky (LUT0-IN2 přes port P11)

První dva jsou AND-ed a oba OR-ed s druhým v LUT0, jehož implementace je konfigurována jako na obrázku 6.

Krok 7: Konfigurace zařízení - vlastnosti komponent Matrix0

Obrázky 7-10 ukazují zbývající okna vlastností komponent patřících Matrix0.

Krok 8: Konfigurace zařízení - obvod Matrix1

Krok 9: Konfigurace zařízení - 3bitový binární čítač

Horní část obvodu obsahuje logické prvky, hlavně 3bitový binární čítač taktovaný výstupem ADC INT, jak již bylo diskutováno. Tento čítač je implementován s celkem „standardním“schématem znázorněným na obrázku 12.

Toto počítadlo je v našem návrhu realizováno pomocí žabek DFF9, DFF10, DFF11 a INV1, LUT4, LUT8. Výstup DFF9 je LSB, zatímco DFF11 je MSB, jak ukazuje obrázek 13.

LUT4 je nakonfigurován jako XOR, zatímco LUT8 provádí logiku AND-XOR na obrázku 12.

Výstupy čítače jdou na tři digitální výstupní piny pro adresování externího analogového multiplexeru.

LUT10 dekóduje kód čítače, když je skenování dokončeno, a přenáší impuls do Matrix0 přes DLY8 a port P12. Toho je jednoduše dosaženo AND-ingováním výstupů čítače, čímž se dekóduje číslo 7 dec (0b111 binární, konec smyčky).

Krok 10: Konfigurace zařízení - 3bitová porovnávací logika

Obrázek 15 ukazuje obvod použitý k detekci, kdy se smyčka iteruje na aktuální adrese „vítěz“. V tomto případě, jak již bylo diskutováno, by měl digitální impuls vynutit opětovné načtení aktuálního výsledku ADC, aby se vyřešila možná situace zablokování.

Adresa „vítěz“je uložena v dočasném registru Matrix1 (viz níže), zatímco aktuální adresa je vydávána binárním čítačem.

Brány XNOR poskytují skutečný (logický 1 nebo „vysoký“) výstup, pokud jsou oba vstupy stejné. AND-ing tento signál pro všechny bity (LUT9) nám dává impuls, když jsou oba binární kódy stejné. Podrobnosti o XOR branách jako paritním checkeru najdete v Reference.

Signál „Counter-equals-Latch“je předán do Matrix0 přes port P11.

Krok 11: Konfigurace zařízení - digitální porovnávací logika a dočasný registr

Spodní část obrázku 11 (zvýrazněná na obrázku 16) ukazuje blok DCMP, rozhodovací část tohoto návrhu.

DFF6, 7 a 8 tvoří 3bitový registr pro uložení dočasného vstupního čísla „vítěz“, když je smyčka spuštěna. Vstupem do klopných obvodů jsou výstupy 3bitových binárních čítačů, jak je vidět na globálním obvodu Matrix1 na obrázku 11, zde z důvodu přehlednosti vynechány.

Výstupy z tohoto registru nemohou řídit přímo 7segmentový displej, protože zde uložená hodnota se během skenování mění a měla by být považována za „platnou“až na konci samotného skenování.

Z tohoto důvodu se výstupy dočasných registrů připojují k smyčkovému registru Matrix0 prostřednictvím intermaticových portů P13, P14 a P15.

Na obrázku 16 je důležité poznamenat, že dočasný registr je taktován výstupem DCMP OUT+, když výsledky porovnání registrů ADC-SPI způsobí nalezení nového maxima.

Stejný signál OUT+ je předáván do Matrix0, SPI CLK Logic, přes port P10.

Krok 12: Konfigurace zařízení - vlastnosti komponent Matrix1

Obrázky 17-19 ukazují okna vlastností komponent patřících Matrix1.

Krok 13: Výsledky

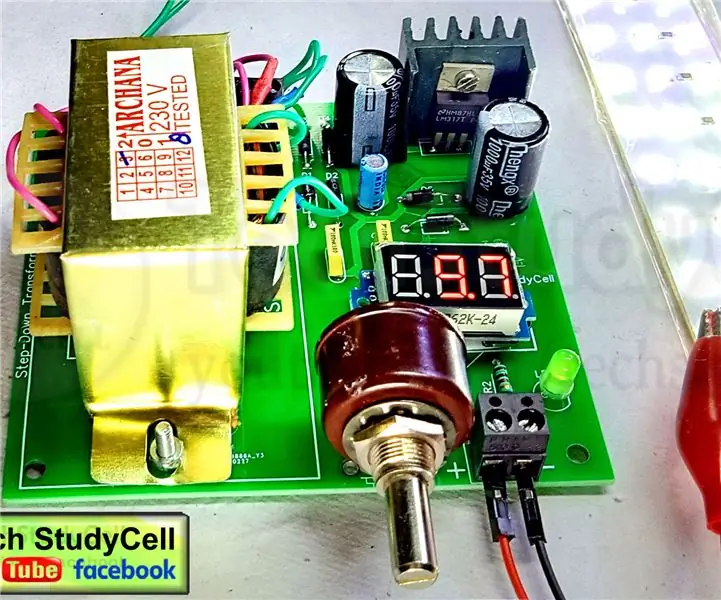

Pro testování implementace byl zkonstruován prototyp zkušební desky, kde je 8 analogových vstupních napětí získáno řadou odporových děličů s TrimPots (jak je znázorněno na obrázku 20).

Použitý multiplexor je ADG508, část, která může pracovat s jediným napájením (12 V).

7segmentový ovladač displeje je 74LS47. Dekóduje paralelní vstupní slovo a přímo pohání 7-segmentový displej se společnou anodou.

Zkušební deska má 2x10 pravoúhlý konektor pro připojení přímo do Advanced Development Platform GreenPAK na jejím rozšiřujícím konektoru, jak je znázorněno na obrázku 21.

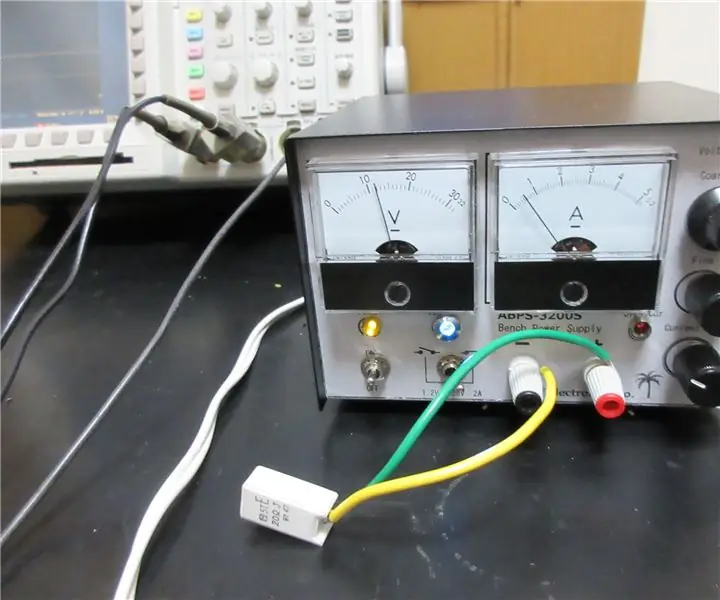

Ve spojení s Advanced Development Platform GreenPAK je velmi snadné provádět měření signálů pro rychlou kontrolu. Obrázek 22 například ukazuje sadu signálů (respektive výstupů CLOCK, ADC INT a DCMP OUT+) zachycených logickým analyzátorem HP 54620A. Křivky jsou vyvolávány stoupající hranou signálu OUT+ (na rozsahu označeném jako „A> B“), proto se jedná o zachycení průběhu, když je mezi analogovými vstupy detekováno nové maximální napětí. Ve skutečnosti to bylo získáno otáčením jednoho z TrimPotů hodnotící rady pro zvýšení odpovídajícího napětí zobrazeného na obrázku 22.

Obrázek 23 ukazuje schéma hodnotící rady.

Závěr

V tomto Instructable jsme implementovali osmikanálový vyhledávač maximálního (nebo min.) Napětí, který bude použit jako společný doplněk vícekanálových řídicích systémů. Prezentovaný přístup využívá pokročilé funkce komponent GreenPAK a ukazuje, jak je možné integrovat do jednoho čipu analogové a digitální funkce. Několik komerčních integrovaných obvodů lze nahradit Dialog GreenPAK, aby bylo možné snížit velikost aplikace a náklady.

Doporučuje:

Monitor napětí pro vysokonapěťové baterie: 3 kroky (s obrázky)

Monitor napětí pro vysokonapěťové baterie: V této příručce vám vysvětlím, jak jsem vytvořil monitor napětí baterie pro svůj elektrický longboard. Namontujte jej, jak chcete, a připojte k baterii pouze dva vodiče (GND a VCC). Tato příručka předpokládá, že napětí vaší baterie překročí 30 voltů

Nastavitelné napětí DC napájení pomocí regulátoru napětí LM317: 10 kroků

DC napájecí zdroj s nastavitelným napětím pomocí regulátoru napětí LM317: V tomto projektu jsem navrhl jednoduché stejnosměrné napájení s nastavitelným napětím pomocí IC LM317 IC se schématem napájecího obvodu LM317. Protože tento obvod má vestavěný můstkový usměrňovač, můžeme na vstup přímo připojit napájení 220 V/110 V AC

8kanálový analogový zesilovač pro PC nebo domácí kino: 12 kroků (s obrázky)

8kanálový analogový zesilovač pro PC nebo HomeTheater: Toto je můj první návod. Naučím vás, jak vytvořit 8kanálový zesilovač pro počítač nebo audio systém se samostatnými analogovými výstupy. Použil jsem jej pro svůj stolní počítač, ke sledování filmů, poslechu hudby HD a hraní her, navíc

DIY analogový variabilní napájecí zdroj s přesným omezovačem proudu: 8 kroků (s obrázky)

DIY analogový variabilní napájecí zdroj s omezovačem přesného proudu: V tomto projektu vám ukážu, jak používat slavný LM317T s výkonovým tranzistorem zesilovače proudu a jak používat zesilovač proudu Linear Technology LT6106 pro přesný omezovač proudu. Tento obvod může umožnit můžete použít až více než 5 A

8kanálový programovatelný časovač: 13 kroků

8kanálový programovatelný časovač: Úvod Pro své projekty používám od roku 1993 řadu mikrokontrolérů Microchip PIC a veškeré mé programování jsem provedl v jazyce assembler pomocí Microchip MPLab IDE. Moje projekty se pohybovaly od jednoduchých semaforů a blikání