Obsah:

- Krok 1: Uživatelská obsluha digitálního sekvenceru

- Krok 2: Technické detaily

- Krok 3: Technické detaily

- Krok 4: 7segmentový dělič hodin

- Krok 5: Dělič hodin za minutu

- Krok 6: Dělič hodinového rozteče

- Krok 7: Play/Pause/Select State Machine

- Krok 8: Play/Pause/Select State Machine

- Krok 9: Výstup FSM

- Krok 10: Výstup FSM

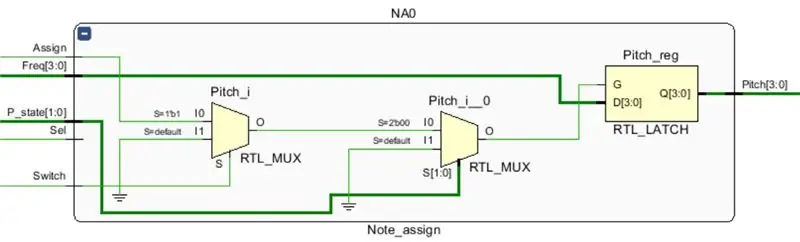

- Krok 11: Přiřazení poznámky

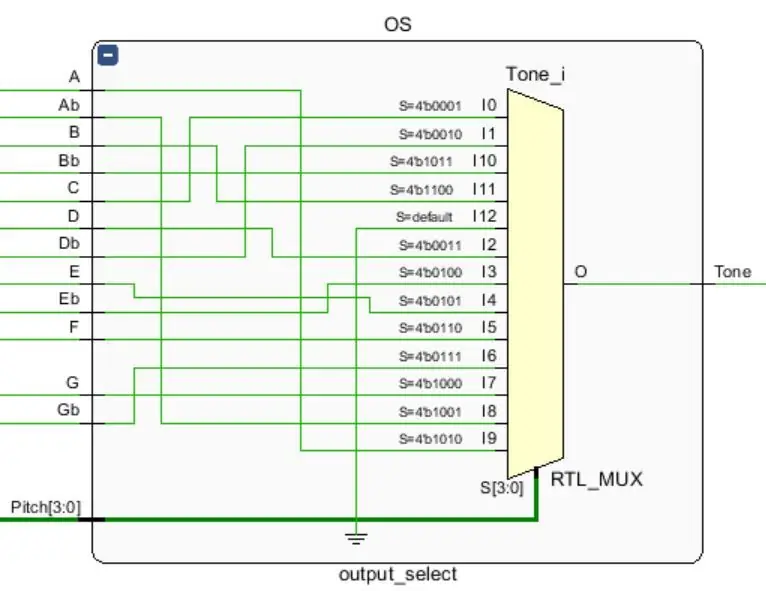

- Krok 12: Výběr výstupu

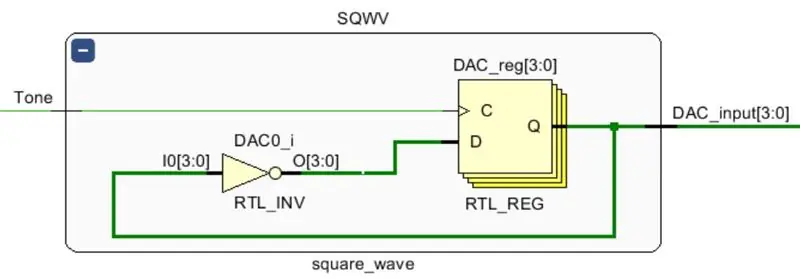

- Krok 13: Square Wave Gen

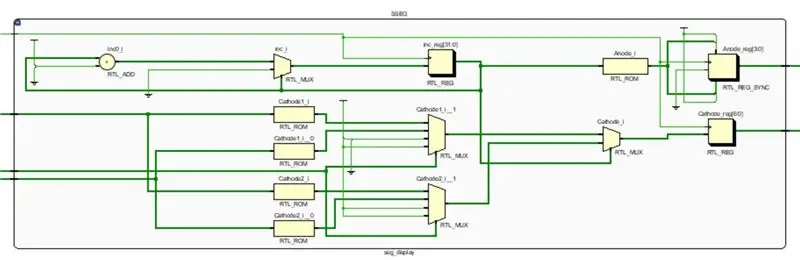

- Krok 14: 7segmentový displej

- Krok 15: Konečný výběr

- Krok 16: Externí zařízení: DAC

- Krok 17: Externí zařízení: reproduktor

- Krok 18: Ukázka videa

- Krok 19: Kód VHDL

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:24.

- Naposledy změněno 2025-01-23 14:38.

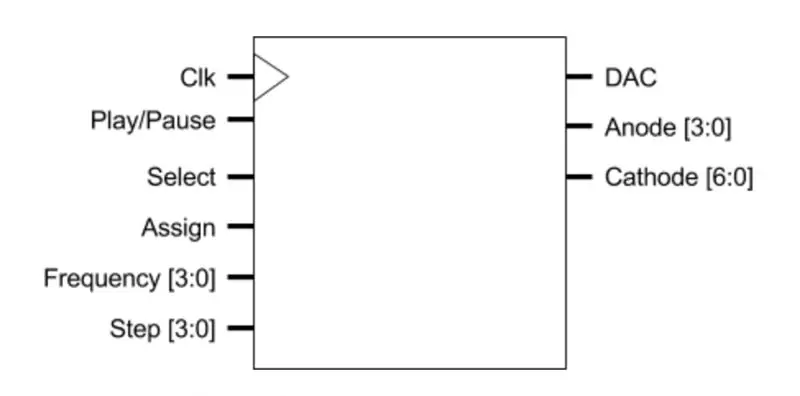

CPE 133, Cal Poly San Luis Obispo

Tvůrci projektu: Jayson Johnston a Bjorn Nelson

V dnešním hudebním průmyslu je jedním z nejčastěji používaných „nástrojů“digitální syntetizátor. Každý hudební žánr, od hip-hopu po pop a dokonce i country, používá ve studiu digitální syntezátor k vytváření beatů a zvuků, které potřebují k oživení své hudby. V tomto tutoriálu vytvoříme velmi jednoduchý syntezátor s deskou FPGA Basys 3.

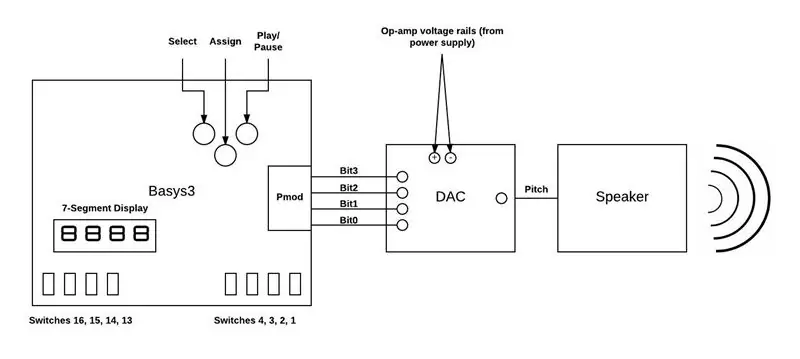

Syntetizátor bude schopen hrát čtyři vybrané čtvrťové noty při konstantním počtu úderů za minutu. Uživatelé použijí přepínače k přiřazení každé noty k hudebnímu tónu. Pro tento projekt používáme 4bitový převodník digitálního signálu na analogový (DAC) k převzetí výstupu z desky a jeho převodu na analogový signál. Výstup z DAC bude poté veden do standardního reproduktoru počítače, čímž vznikne naše hudba. Je možné šestnáct diskrétních hřišť. Náš syntezátor omezíme na jednu oktávu o 12 notách, které spadají mezi střední C (261,6 Hz) a B4 (493,9 Hz). Uživatel bude mít také možnost přiřadit více not současně, stejně jako přiřadit odpočinek stisknutím přiřadit, přičemž žádný z přepínačů výšky nebude posunut nahoru. Při výběru a přehrávání každé noty se na 7segmentovém displeji zobrazí nota s písmeny. Budeme také používat tři tlačítka na desce, jedno pro přehrávání a pozastavení hudby, jedno pro resetování syntezátoru a jeho uvedení do režimu „výběru“a třetí pro přiřazení každé noty výšky v režimu výběru.

Jakmile je uživatel spokojen s výběrem not a po stisknutí tlačítka přehrávání, syntetizér bude opakovaně přehrávat každou notu, dokud uživatel nestiskne pauzu nebo nevybere.

Zde je seznam požadovaného vybavení:

- Vivado (nebo jakýkoli pracovní prostor VHDL)

- Basys 3 nebo podobná deska FPGA

- Převodník digitálního signálu na analogový (min. 4 bity)

- Reproduktor s konektorem pro sluchátka

- Drátové vývody

Krok 1: Uživatelská obsluha digitálního sekvenceru

Následující kroky slouží k ovládání digitálního sekvenceru. Digitální sekvencer podporuje přehrávání 12 různých výšek (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), které se pohybují od 261,6 Hz do 493,9 Hz.

1. Stisknutím levého tlačítka přepnete desku do režimu výběru. V tomto režimu budou k uložení odlišné hodnoty výšky použity každý 4 spínače úplně vlevo (přepínače 13 až 16).

2. Chcete -li provést výběr, zapněte jeden z levých přepínačů a poté pomocí 4 pravých přepínačů (přepínače 1 až 4) vyberte požadovanou výšku. Rozteč spojená se specifickou kombinací pravých spínačů se zobrazí na sedmisegmentovém displeji a displej se aktualizuje na novou přidruženou výšku, kdykoli jsou pravé přepínače posunuty do nové kombinace. Zbytek lze přiřadit tak, že nikdy nepřiřadíte výšku tónu jednomu z levých přepínačů nebo přiřadíte výšce zobrazené jako 0 na displeji k notě. Jakmile je požadovaná výška nalezena a je zobrazena na displeji, stisknutím spodního tlačítka přiřazení přiřaďte notu konkrétní výšku.

3. Opakujte krok 2 pro tři zbývající noty tak, že každý ze zbývajících levých přepínačů přepnete jednotlivě, pravým tlačítkem vyberete příslušnou výšku a stisknutím spodního tlačítka přiřadíte výšku notě. Více tónů lze přiřadit stejné výšce posunutím více než jednoho levého přepínače nahoru.

4. Nyní, když jsou přiřazeny všechny výšky tónů, je digitální sekvencer připraven hrát. Chcete -li přehrát poznámky na reproduktoru, pouhým stisknutím pravého tlačítka přehrávání/pozastavení zahájíte přehrávání hudby. Pořadí sekvence přehrávání zrcadlí výšky spojené s levými přepínači zleva doprava. Noty se budou hrát se stanoveným počtem úderů za minutu v pořadí 1, 2, 3, 4, 1, 2…. Během přehrávání hudby na displeji se na displeji zobrazí poznámka, která právě hraje. Chcete -li přehrávání hudby pozastavit, jednoduše stiskněte pravé tlačítko. Poté se hudba zastaví a na displeji se zobrazí symbol pauzy. Opětovným stisknutím pravého tlačítka přehrávání obnovíte.

Krok 2: Technické detaily

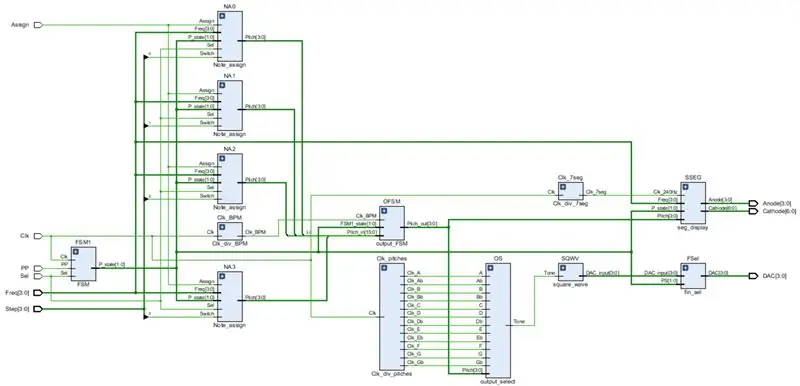

Náš syntezátor využívá mnoho různých digitálních komponent. Zahrnuty jsou stroje s konečným stavem, registry, multiplexory, děliče hodin a další. K sestavení našeho syntetizátoru jsme použili 10 unikátních modulárních souborů. Spíše než dělat z každého modulu součást, jsme rozdělili modulární soubory podle funkcí. Většina modulů je ve výsledku více než jednou komponentou. Všimněte si, že výše uvedený obrázek ukazuje každý blok svázaný dohromady v našem špičkovém designu.

Každý modul probereme popisem vstupů a výstupů, rozdělením jeho komponent a vysvětlením jeho účelu v celkovém návrhu. V dolní části instruktovatelného souboru je zahrnut soubor ZIP, který obsahuje každý soubor kódu VHDL použitý v projektu.

Vstupy

- Clk (nativní hodinový signál)

- PP (přehrávání/pauza)

- Sel (dát syntetizátor do režimu výběru)

- Přiřadit (přiřadit krok k rozteči)

- Krok (poziční poznámky)

- Freq (přepínače vytvářející požadovanou výšku)

Výstupy

- Anoda (7segmentové anody)

- Katoda (7segmentové katody)

- DAC (4-bitové řízení DAC)

Krok 3: Technické detaily

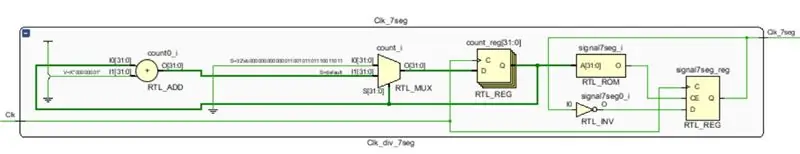

Krok 4: 7segmentový dělič hodin

Náš syntetizátor využívá tři děliče hodin, z nichž všechny produkují signály, které v našem projektu slouží jinému účelu. Dělič hodin přijímá nativní hodinový signál a vytváří pozměněný signál, který má frekvenci nižší než původní hodinový signál. Nativní takt Basys 3 je 100 MHz. Toto je frekvence, kterou naše děliče hodin využívají. Pokud používáte jinou desku FPGA s jinou nativní taktovací frekvencí, možná budete muset kód změnit.

7segmentový dělič hodin produkuje signál, který pohání soubor seg_display. Jak tento soubor funguje, vysvětlíme podrobněji, když se dostaneme do jeho sekce. Tento dělič hodin v zásadě produkuje signál 240 Hz, který bude použit k přepínání mezi anodami a katodami na displeji. Signál je 240 Hz, protože frekvence, při které lidské oko nedokáže rozpoznat nepřítomnost světla, je 60 Hz. Používáme dvě číslice, takže zdvojnásobením této frekvence bude každá číslice oscilovat při 60 Hz. Poté jej zdvojnásobíme, abychom získali 240 Hz, protože systém se mění pouze tehdy, když je signál vysoký, nikoli když klesá.

Aby toho bylo dosaženo, dělič využívá nativní signál 100 MHz a počítá s každou stoupající hranou. Když čítač dosáhne 416667, výstup přejde z nízké na vysokou nebo naopak.

Vstupy

Clk (nativní hodinový signál)

Výstupy

Clk_7seg (k seg_display)

Komponenty

- D registr

- MUX

- Měnič

- Zmije

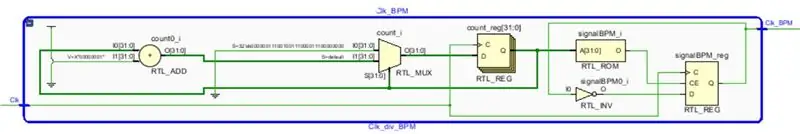

Krok 5: Dělič hodin za minutu

Dělič hodin BPM funguje podobným způsobem. Tento dělič vytváří hodinovou frekvenci, která řídí přepínání mezi čtyřmi kroky při výstupu tónů ve stavu přehrávání. Rozhodli jsme se přepínat mezi notami na 100 BPM. Při 100 BPM se každá nota bude hrát po dobu 3/5 sekundy. Výsledný signál by měl frekvenci 1,67 Hz.

K vytvoření signálu této frekvence jsme opět použili systém počítání, ale tentokrát byl počet 60 milionů. Pokaždé, když počítadlo dosáhne 60 milionů, výstupní signál se bude přepínat vysoko nebo nízko.

Vstupy

Clk (nativní taktovací frekvence)

Výstupy

Clk_BPM (to output_FSM)

Komponenty

- D registr

- MUX

- Měnič

- Zmije

Krok 6: Dělič hodinového rozteče

Oddělovač hodin Pitches je největší z našich děličů hodin. Tento dělič vydává 12 různých signálů odpovídajících 12 různým notám, které může náš syntezátor hrát. Pomocí základních znalostí hudební teorie jsme usoudili, že bit nebo sběrnice mohou oscilovat rychlostí, která odpovídá frekvenci not. Chcete -li zobrazit frekvence, které jsme použili, podívejte se sem. Použili jsme čtvrtou oktávu výšek.

Zde se používá stejný systém počítání. Konkrétní hodnoty, které jsme započítali, najdete v souboru označeném Clk_div_pitches.

Vstupy

Clk (nativní taktovací frekvence)

Výstupy

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (to output_select)

Komponenty

- D registr

- MUX

- Měnič

- Zmije

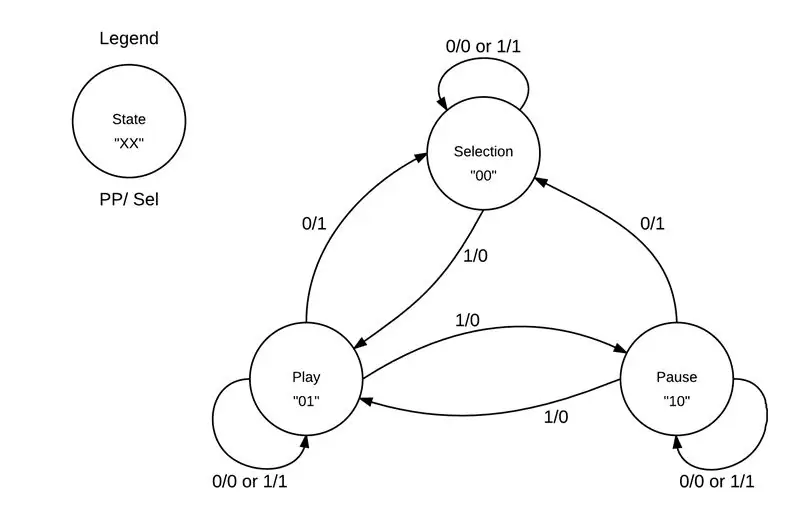

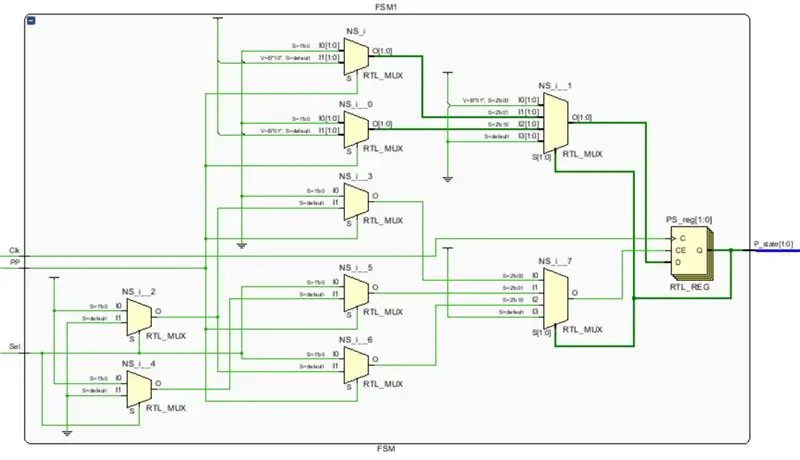

Krok 7: Play/Pause/Select State Machine

V našem projektu jsou dva stroje s konečným stavem (FSM). FSM je logické zařízení, které může existovat pouze v jednom stavu z konečného množství stavů. Pomocí FSM se digitální obvod může přesunout do nového stavu na základě kombinace vstupů. Pomocí vstupní logiky se stav FSM změní, když je stoupající hrana hodin. Ze stavu a vstupů do obvodu můžete vytvořit logiku výstupu, která dává výstupy, které existují pouze v případě, že je FSM v určitém stavu.

Stavový stroj PPS je první FSM v našem obvodu. V tomto FSM jsou tři stavy; Režim přehrávání, pozastavení a výběr. K procházení různými stavy jsme použili tlačítka PP a Výběr. Podívejte se na stavový diagram výše, abyste zjistili, jak dochází k přechodům mezi stavy. Tento přechod FSM jsme provedli na náběžné hraně nativních hodin 100 MHz, takže by bylo nemožné, aby stroj nepřešel, když bylo stisknuto jedno z tlačítek, a to i po velmi krátkou dobu. Současný stav (P_state) je jediným výstupem z tohoto modulu.

Vstupy

- Clk (nativní taktovací frekvence)

- Sel (levé tlačítko)

- PP (pravé tlačítko)

Výstupy

P_state (současný stav, na output_FSM, note_ assign, seg_dsiplay, final_select)

Komponenty

- MUX

- D registr

Krok 8: Play/Pause/Select State Machine

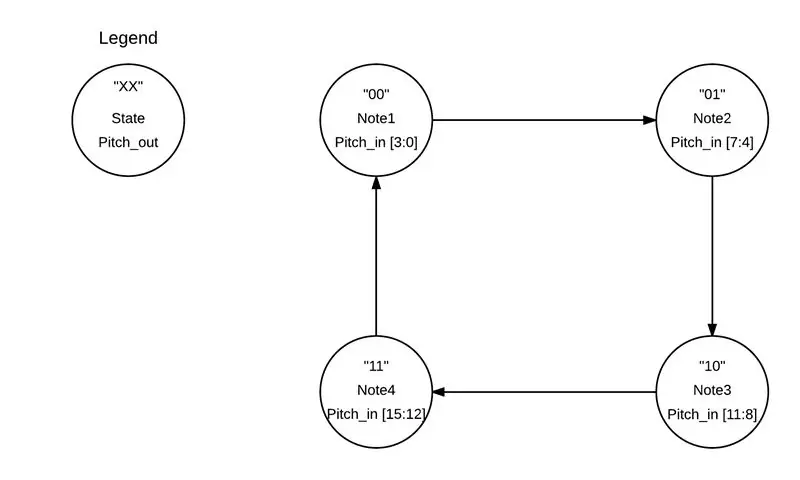

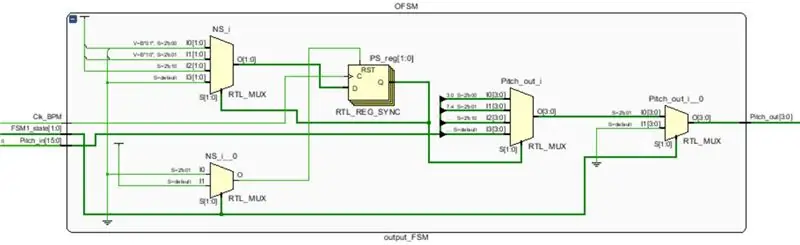

Krok 9: Výstup FSM

Toto je druhý FSM, na který se odkazuje v předchozí části. Tento FSM má jinou funkci než ostatní, ale jeho základ je v zásadě stejný.

Výstupní FSM funguje pouze tehdy, je -li současný stav z prvního FSM „01“(stav přehrávání). V zásadě se jedná o povolení modulu. Pokud je stav „01“, pak FSM přepíná mezi stavy na náběžné hraně hodinového signálu BPM. Děláme to proto, že output_FSM řídí, které binární číslo pro vybrané hřiště bude odesláno do modulů output_select a seg_display. FSM má 16bitový vstup pocházející z modulu pro přiřazení not, který bude popsán dále. Ve stavu „00“pro output_FSM modul vydá „xxxx“pro první přiřazenou notu. Potom v „01“vydá „yyyy“pro druhou notu a tak dále pro každou notu, než se vrátí zpět k první notě. Viz stavový diagram výše.

Tento FSM se liší od prvního, protože neexistuje žádná logika vstupu pro ovládání přepínání mezi stavy. Místo toho bude FSM fungovat pouze tehdy, když je stav z prvního FSM "01", a pak tento FSM bude přecházet mezi stavy pouze na stoupající hraně hodinového signálu. Dalším rozdílem je, že tento modul má výstupní logiku, což znamená, že nevydává aktuální stav, ale vydává binární číslo pro výšku v tomto stavu.

Vstupy

- Clk_BPM (hodinový signál BPM z děliče hodin)

- FSM1_state (PS z PPS FSM)

- Rozteč

Výstupy

Pitch_out (po jedné výšce, na output_select a seg_display)

Komponenty

- MUX

- D registr

Krok 10: Výstup FSM

Krok 11: Přiřazení poznámky

Modul přiřazení not je zodpovědný za skutečné přiřazení výšky poziční notě nebo kroku. Tento modul je ve skutečnosti docela jednoduchý. Nejprve zkontroluje, zda je obvod ve stavu „výběru“a zda je krokový spínač (zcela vlevo) vysoko. Pokud je to pravda a tlačítko přiřazení je stisknuto, výstup modulu se bude rovnat binárnímu číslu reprezentovanému frekvenčními spínači (zcela vpravo).

Původně jsme se pokoušeli vytvořit modul, který by ve skutečnosti uložil jeden ze signálů hodinového tónu na výstup, ale došlo k problémům se změnou výstupu tak, aby sledoval signály vstupních hodin. Toto je jediný modul použitý ve finálním návrhu více než jednou. Ke každému kroku je přidružen modul note_assign, a proto každá instance modulu získá jeden bit sběrnice Step.

Vstupy

- P_state (současný stav z PPS FSM)

- Sel (levé tlačítko)

- Přepínač (jednokrokový přepínač)

- Freq (krajní pravé přepínače pro výšku)

- Přiřadit (spodní tlačítko, přiřadí poznámku)

Výstupy

Rozteč (binární číslo, na výstup_FSM)

Komponenty

- MUX

- D registrovat

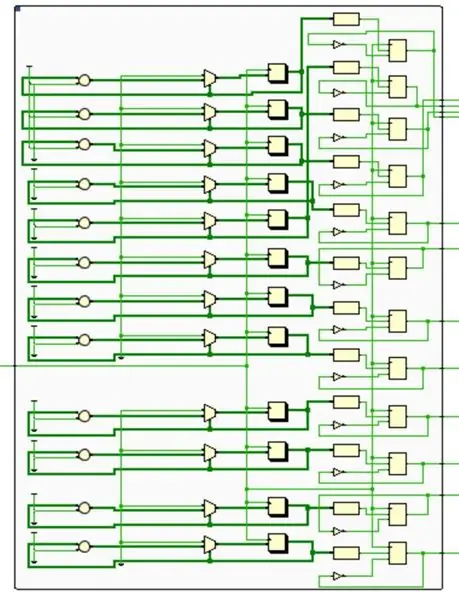

Krok 12: Výběr výstupu

Výběr výstupu je zodpovědný za převzetí binárního čísla pro hřiště a jeho připojení k příslušnému hodinovému signálu. I přes svou velikost se jedná o relativně jednoduchý modul. Output_select je v podstatě binární dekodér, dekódující binární číslo pro výšku na konkrétní hodinový signál. Vlastně přiřazení výstupu k hodinové frekvenci zde fungovalo lépe ve srovnání s modulem note_ assign, protože tento modul musel pouze MUXOVAT hodinové signály s binárním číslem představujícím řídicí vstup.

Omlouváme se za podivné směrování, Vivado uspořádal signály výšek abecedně pro soubor clk_div_pitches, ale pro tento soubor je uspořádal vzestupně binárním číslem, což způsobilo, že výšky jsou v jiném pořadí. Všimněte si také, že pokud bylo binární číslo z output_FSM „0000“nebo cokoli většího než „1100“, pak MUX odeslal plochý signál „0“.

Vstup

- Rozteč (z output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (signály hodinového tónu)

Výstup

Tón (jeden bit, který odpovídá vybranému hodinovému signálu, na square_wave)

Komponenty

MUX

Krok 13: Square Wave Gen

Modul square_wave je generátorem čtvercové vlny, která je vyvedena z desky do DAC. Pomocí tónového signálu z předchozího souboru tato square_wave invertuje 4bitové číslo mezi „0000“a „1111“na stoupající hraně Tónu. Tón je specifická frekvence kmitočtu, takže square_wave produkuje vlnu s jinou frekvencí, když output_FSM přechází do jiného stavu. 4bitový výstup z tohoto modulu jde do modulu fin_sel, kde logika určuje, zda bude tato sběrnice vydávána na základě stavu z PPS FSM.

Alternativou k tomuto generátoru čtvercových vln je produkce sinusové vlny. I když by to s největší pravděpodobností přineslo lepší konečný tón, jeho implementace je podstatně obtížnější, proto jsme se rozhodli generovat pouze čtvercovou vlnu.

Vstupy

Tón (oscilační bit z output_select)

Výstupy

DAC_input (oscilační 4bitová sběrnice, která se mění se stejnou frekvencí tónu)

Komponenty

- Měnič

- D registr

Krok 14: 7segmentový displej

Modul seg_display ovládá 7segmentový displej na základní desce. V rámci modulu dochází ke dvěma procesům. První proces dekóduje Freq, když je ve stavu „výběr“, nebo Pitch, když je v režimu „přehrávání“. V režimu „pauza“modul dekóduje, aby zobrazil symbol pauzy. Při pohledu na kód VHDL můžete vidět, že binární dekodér ve skutečnosti dekóduje vstup na dva různé signály, katodu1 a katodu2. Katoda 1 představuje písmeno odpovídající výšce, která se má zobrazit, a katoda 2 představuje plochý symbol (b), pokud existuje. Důvod se týká druhého procesu provedeného modulem seg_display.

Na desce basys3 má segmentový displej společné katody. Zatímco anody ovládají, která číslice je zapnutá, katody ovládají, které segmenty jsou zapnuté. Vzhledem k tomu, že displej má běžné katody, znamená to, že můžete současně zobrazit pouze jednu sadu segmentů. To pro tento projekt představuje problém, protože chceme současně zobrazit písmeno na první číslici a plochý symbol. Nyní si pamatujete hodinový signál 7seg? Abychom tento problém vyřešili, měníme anody a katody tam a zpět na hodinovém signálu 7seg. Protože hodinový signál je 240 Hz a používáme dvě číslice, každá číslice bude oscilovat při 60 Hz. Lidskému oku to bude připadat, že číslice vůbec nekmitají.

Všimněte si také, že displej desky basys3 používá negativní logiku. To znamená, že pokud je anoda nebo katoda nastavena na '0', tato číslice nebo segment bude zapnutý a naopak.

Vstupy

- Rozteč (binární číslo pro notu, používané ve stavu přehrávání)

- Freq (frekvenční spínače, používané ve stavu výběru)

- P_state (současný stav z PPS FSM)

- Clk_240Hz (hodinový signál z Clk_div_7seg, dvojnásobek 120, protože používáme pouze náběžnou hranu)

Výstupy

- Katoda (sběrnice, která ovládá segmenty na displeji, konečný výstup)

- Anoda (sběrnice, která ovládá číslice na displeji, konečný výstup)

Komponenty

- Západka

- MUX

- D registr

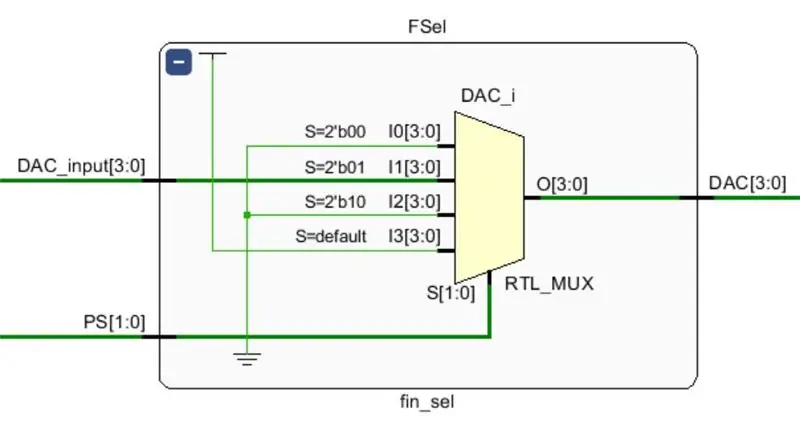

Krok 15: Konečný výběr

Final select je posledním modulem použitým v tomto projektu. Další jednoduchý modul, tento modul ovládá konečný výstup, který bude směřovat do DAC. Ve stavu „výběr“nebo „pauza“modul vydá statický „0000“, takže z reproduktorů nebude přehrávána žádná hudba. Ve stavu „přehrávání“bude modul vydávat oscilační 4-bity určené square_wave.

Vstupy

- P_state (současný stav z PPS FSM)

- DAC_input (oscilační 4 bity z square_wave)

Výstupy

DAC (rovná se DAC_input ve stavu přehrávání, konečný výstup)

Komponenty

MUX

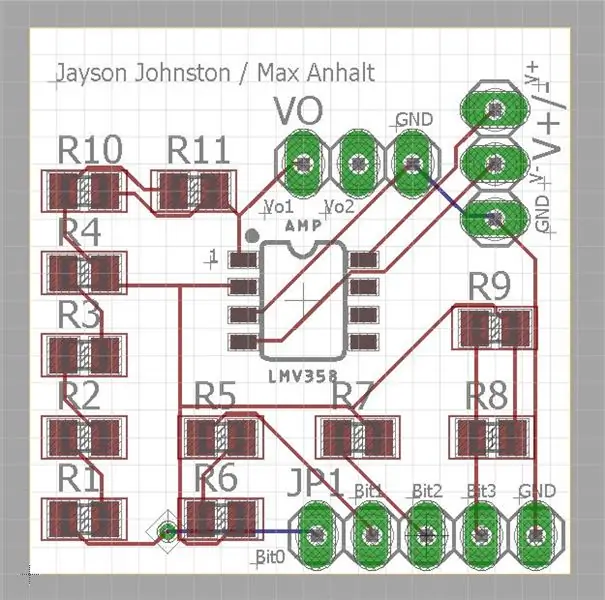

Krok 16: Externí zařízení: DAC

Převodník digitálního signálu na analogový (DAC) převádí diskrétní signál a převádí jej na spojitý signál. Náš DAC má čtyři bity a je vyroben ze součtového zesilovače. Použitím poměru rezistorů v napájecí a zpětnovazební smyčce jsme byli schopni vytvořit systém, který výstupy na 16 různých úrovních vytváří „součtem“každé větve. Bit0, horní větev, nese nejmenší váhu a když je vysoká, přispívá nejmenším potenciálem, protože má vyšší odpor. Hmotnost klesá, když jdete po větvích dolů. Pokud byste počítali binárně nahoru a potom dolů pomocí bitových vstupů, výstupní napětí by vypadalo jako kroková sinusová vlna. Vstup pro DAC byl připojen k jednomu z PMOD na desce pro přenos 4bitového signálu.

DAC byl původně sestaven pro třídu elektrotechniky a byl navržen a pájen námi, nikoli zakoupen v obchodě. Nahoře je obrázek souboru návrhu pro vytvoření desky s plošnými spoji.

Krok 17: Externí zařízení: reproduktor

Pro tento projekt nebudete chtít koupit super pěkný pár reproduktorů. Jak můžete říci, zvuk je docela základní. Šli jsme a koupili si sadu reproduktorů k počítači od Best Buy za 8 $. Cokoli s konektorem pro sluchátka funguje dobře. Monotónní funguje také dobře. Můžete dokonce použít sluchátka, ale můžete je vyhodit!

Pro připojení výstupu DAC k reproduktorům jsme použili propojovací kabely a poté jsme přidrželi výstupní kabel na špičce konektoru pro sluchátka a kabel pro uzemnění k základně. Pokusili jsme se pomocí elektrické pásky držet kabely na místě, ale způsobovalo to velké rušení. Tento problém by mohl vyřešit pokus o jiný styl pásky.

U našich reproduktorů jsme je přepnuli na nejvyšší nastavení a dostali jsme slušně hlasitý šum.

A to je poslední krok k vytvoření digitálního sekvenceru z desky FPGA! Přejděte do dalších dvou částí, stáhněte si celý náš kód VHDL a podívejte se na sekvencer v akci.

Krok 18: Ukázka videa

Toto video ukazuje konečnou verzi pracovního projektu, včetně procesu přiřazení přepínačů ke 4 odlišným výškám a reproduktorů hrajících příslušné noty.

Krok 19: Kód VHDL

Zde je kód pro celý projekt, včetně omezení a sim souborů použitých při stavbě sekvenceru. Všimněte si toho, že to v architektuře říkají nepoužité soubory návrhu.

Doporučuje:

Sekvencer sekce rytmu Arduino MIDI: 8 kroků (s obrázky)

Sekvencer Arduino MIDI Rhythm Section: Mít dobrý softwarový bicí automat je dnes snadné a levné, ale používání myši mi zabíjí zábavu. Proto jsem si uvědomil, co bylo původně zamýšleno jako čistý 64krokový hardwarový MIDI bubnový sekvencer schopný spustit až 12 různých bicích elem

Jednoduchý sekvencer: 16 kroků (s obrázky)

Simple Sequencer: Jedním z klíčů k vytváření dobré hudby je bezmyšlenkovité opakování. V tom je jednoduchý sekvencer skvělý. Dělá to samé znovu a znovu v sekvenci osmi not. Můžete upravit frekvenci poznámky, dobu trvání poznámky a

Sekvencer piva: 7 kroků

Beer Sequencer: Cos'èIl Beer Sequencer è un sequencer a sedici step attivabili tramite dei pesi. I pesi possono Essere disposti negli appositi aloggiamenti che contengono gli FSR (force sensing resistor) utilizzati per la detezione e variazione del peso. La variaz

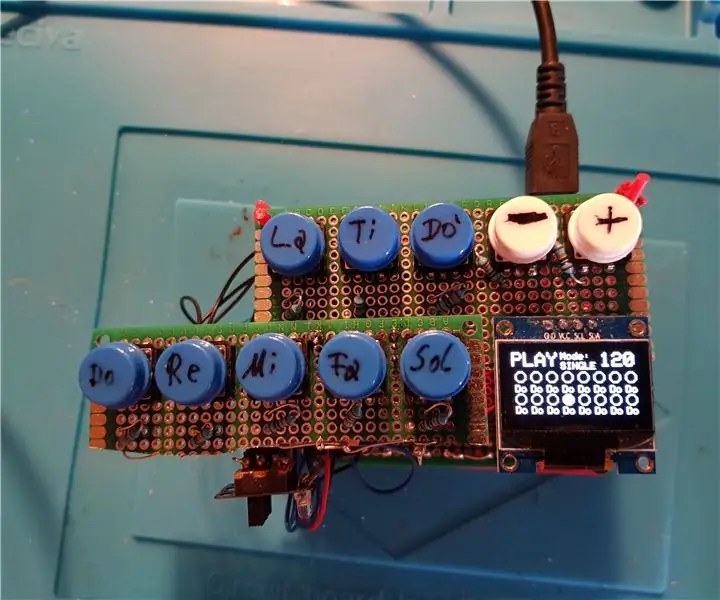

DoReMiQuencer - Programovatelný MIDI sekvencer s klávesnicí: 7 kroků

DoReMiQuencer - Programovatelný MIDI sekvencer s klávesnicí: Toto zařízení bylo vytvořeno pro použití s VCVRack, virtuálním modulárním syntezátorem vytvořeným VCV, ale může sloužit jako MIDI řadič pro obecné účely. Slouží jako MIDI sekvencer nebo klávesnice, v závislosti na zvoleném režimu. MIDI noty mapované na klíč

Programovatelný RGB LED sekvencer (pomocí Arduino a Adafruit Trellis): 7 kroků (s obrázky)

Programovatelný RGB LED sekvencer (pomocí Arduina a Adafruit Trellis): Moji synové chtěli barevné LED pásky, aby osvětlily jejich stoly, a já jsem nechtěl používat konzervovaný RGB páskový ovladač, protože jsem věděl, že se s pevnými vzory nudí tyto ovladače mají. Také jsem si myslel, že by to byla skvělá příležitost vytvořit