Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:18.

- Naposledy změněno 2025-01-23 14:38.

V minulosti jsem sepsal průvodce, jak postavit počítač na bázi Z80, a obvod jsem navrhl tak, aby byl co nejjednodušší, aby jej bylo možné postavit co nejsnadněji. Napsal jsem také malý program se stejnou myšlenkou jednoduchosti. Tento design fungoval docela dobře, ale nebyl jsem s ním úplně spokojený. Začal jsem přepisováním programu, který umožnil jeho programování za běhu. To mi umožnilo vyzkoušet kousky kódu, aniž bych jej musel věnovat EEPROM, což by zase vyžadovalo přeprogramování EEPROM. To mi nepřišlo jako zábavný nápad. Pak jsem začal přemýšlet o paměťových prostorech. Pokud bych chtěl propojit kus hardwaru (hlavně IO), kus kódu by potenciálně mohl překročit množství místa v paměti, které má systém k dispozici. Pamatujte, že design používal pouze spodní bajt adresové sběrnice a poté byl pro výběr mezi mezerami ROM a RAM použit spodní bit vysokého bajtu. To znamenalo, že jsem měl k použití pouze 253 bajtů prostoru. Možná se ptáte, proč 253 místo 256. Důvodem je, že můj nový kód vstřikuje tři bajty dat na konci napsaného programu (to bude popsáno později, když jsem jej upravil tak, aby fungoval na novém designu).

n

Vrátil jsem se zpět ke svým starým schématům, abych viděl, co se ještě děje. Našel jsem malou vadu obvodu pro výběr paměti, kterou zakryji, až se tam dostanu. Zjednodušená verze: všechny požadavky na zápis by ve skutečnosti prošly, i když byly vždy vloženy do paměti RAM. Zřejmě to nebylo důvodem k obavám, ale tentokrát jsem to chtěl udělat pořádně. A s tím jsem začal kreslit nové schéma. Dva obrázky připojené k této stránce jsou před a po skutečném obvodu. Vyčistil jsem tolik kabelů od špaget, to není sranda.

n

Pokud jste se řídili mým původním podáním a plánujete se řídit tímto, budete mě nenávidět. Pokud začínáte znovu, máte štěstí. Stačí uchopit součásti v seznamu (nebo jejich ekvivalent) a pokračovat.

Zásoby:

LM7805 - 5voltový regulátor Z80 - CPU; mozky systémuAT28C64B - EEPROM. „Trvalé“úložiště dat používané pro firmware počítačeIDT6116SA - SRAM; slouží k ukládání uživatelského kódu a /nebo obecného ukládání datNE555 - Systémové hodiny74HC374 - Oktální D -západka s /OE; používá se jako vstupní čip74LS273 - Octal D -Latch with /MR; výstupní čip TLC59211 - čip ovladače LED (používá se, takže 74LS273 může napájet diody LED, protože sám není schopen aktuálního výstupu) MC14572 - Jedná se o čip „Line Driver“, ale zjistil jsem, že je ideální pro logiku řízení paměti. Má 4 střídače a bránu NAND a NOR vestavěnou v 74LS32 - Quad OR gateCD4001 - Quad NOR gateCD4040 - 12 stupňový čítač zvlnění; Nakreslený, ale ne implementovaný dělič hodin (pro provoz systému při nižších taktech) 2 odpory 10K Ohm - Jeden je použit v časovacím obvodu 555, takže pro něj použijte jakoukoli hodnotu, kterou chcete 4 4 Rezistory 1K Ohm - Jeden se používá pro Obvod časovače 555, takže použijte, co chcete. Další se používá pro napájení LED diod, takže ji také změňte, pokud chcete 8x330 Ohm odporová sběrnice 8x10K ohm odporová sběrnice LED 11 - tři se používají pro stav systému a dalších osm jsou výstupy. Pro 8 jsem použil sloupcový graf (HDSP -4836) 4 kondenzátory - dva jsou použity LM7805; 0,22uF a 0,1uF. Jedním z nich je časovač 555, takže použijte to, co považujete za správné. Poslední je pro reset při zapnutí; 100uF2 N. O. Tlačítka - jedno slouží pro vstup, druhé pro reset 8 SPST DIP přepínačů - vstup dat; Použil jsem Piano Key styleWire. Hodně a hodně drátu

n

POZNÁMKA: Verze MC14572 skrz otvor je zastaralá, ale verze SMD je stále aktivní (dokonce ani stav „není pro nový design“), takže možná budete muset zakoupit desku s obvody, abyste ji mohli používat. Místo MC14572 lze použít druhý 74LS32 (viz schéma „obvodu výběru paměti“předchozího)

Krok 1: Rychlý přehled změn + schémata

Jak číst schémata: Šipka namířená na čip je vstup: Vstup> -Šipka směřující od čipu je výstup: Výstup <-Busy používají místo šipky řádek: Bus |-

n

Většina žetonů byla vylosována s přesnými vývody. Na těchto žetonech byl nakreslen malý pokles. Většina čipů má také čísla pinů a štítky. Mohou být trochu těžko čitelné. Moje tužka byla matná.

n

Pokud jde o zapojení obvodů, rozložení nového designu se od původního většinou nezměnilo. Připojil jsem spodní nibble adresního vysokého bajtu k pamětím a poté použil nízký bit horního nibble (A12) pro výběr RAM/ROM. To znamenalo, že ROM prostor šel z 0000-00FF až na 0000-0FFF. Prostor RAM se změnil z 0100-01FF na 1000-1FFF. Také jsem pro lepší design vyměnil logiku řízení paměti a přidal dvě nové stavové LED (a nějakou logiku lepidla). Také jsem nakreslil (ale nezapojil) obvod děliče hodin. Mělo plnit dvě funkce. Zjevnou funkcí je rozdělit frekvenci hodin dolů. Další funkce je pro účely PWM (Pulse Width Modulation), protože 555 nevytváří vlny s 50% pracovními cykly. Na tom v tomto obvodu nezáleží, ale pokud byste chtěli použít hodiny k pohonu některých LED, určitě si všimnete efektů (jedna (sada) LED bude slabší než druhá). Celý zbytek obvodů je v podstatě beze změny.

Krok 2: CPU, paměť a ovládání paměti

Toto je část, kde mě čtenáři mé předchozí verze nenávidí. V původní verzi jsem trochu hodil díly na desku na místo, které vypadalo, že by s připojením neměly problém. Výsledek vypadal, jako by na něj někdo vysypal talíř se špagetami a byl jako „dráty!“Chtěl jsem to trochu vyčistit, takže jsem začal roztrhat vše kromě CPU, RAM a ROM. Vytáhl jsem téměř celý vstupní obvod, výstupní obvod a logiku lepidla. Málem mě to bolelo, ale bylo to nutné. Všechna datová připojení jsem nechal neporušená a spodní bajt adresové sběrnice. Poté jsem připojil další čtyři bity adresové sběrnice (A8-A11) k čipu ROM. Tentokrát jsem se postaral o to, abych čip obešel, aby bylo snazší vytáhnout pro přeprogramování. Také jsem přeskočil připojení adresy dolů na čip RAM.

n

Když to bylo z cesty, musel jsem teď zapojit logiku řízení paměti. V původním schématu jsem připojil linku procesoru /MREQ přímo k /CE k oběma paměťovým čipům, poté jsem připojil /WR k RAM /WE. Pak jsem měl logicky OR’dd CPU /RD a /MREQ a také A9. V zásadě to bylo nastaveno tak, že všechny požadavky na paměť aktivovaly RAM i ROM, ale A9 byl použit k výběru, který z čipů /OE byl vybrán. To bylo v pořádku a to vše proto, že čipy zůstaly neaktivní, dokud nebyl podán požadavek na paměť a poté byl během požadavku na čtení aktivní pouze jeden /OE. To zabránilo přeslechu, ale zavedlo nepříjemnou nuanci. Protože A9 byl použit pouze k určení, který čip odesílá data, a protože CPU měl přímý přístup k pinu RAM /WE, všechny požadavky na zápis by prošly. To bylo v pořádku pro ROM, protože jeho režim zápisu je blokován vázáním /WE přímo na 5V napájení. RAM by však byla zapsána bez ohledu na A9. To znamenalo, že pokus o zápis do místa v paměti ROM zapíše na stejné místo v prostoru RAM.

n

Jedním z řešení by bylo přepojit řídicí logiku tak, aby měl CPU přímý přístup k pinům /OE a /WE čipů a poté pomocí MREQ a A12 vybrat, které čipy /CE byly řízeny. Šel jsem s touto myšlenkou, ale místo toho, abych použil čtyři brány NOR a střídač jako původní design, našel jsem nepříjemný malý čip, který byl pro tento úkol ideální. Musel jsem vytvořit obvod, který používal pouze logické brány dostupné v čipu, ale to bylo dost snadné. A12 se napájí přímo do brány NAND a brány NOR. /MREQ se přivádí do brány NOR a její kompliment se přivádí do brány NAND. Brána NAND se používá k pohonu /CE pro RAM a výstup NOR je převrácen a použit k pohonu ROM /CE. Díky tomu musí být /MREQ nízké před tím, než je vybrán jeden z čipů, a poté A12 vybere, který bude vybrán. S tímto nastavením nyní žádné požadavky na zápis do ROM nic neudělají. Šetří také energii, protože místo obou je aktivní pouze jeden čip. Pokud jde o samotný logický čip, stále máme uvnitř dva nepoužívané měniče. Jeden si později zvykne, ale my se tam dostaneme, až se tam dostaneme.

Krok 3: LED diody stavu systému

Než jsem zahájil tento projekt, pokoušel jsem se propojit s určitým integrovaným obvodem, ale měl jsem s tím potíže. Nejsem si jistý, co se děje, použil jsem sondu LED pro montáž na panel (jedna z těch sestav, která má vestavěný odpor). To mi dalo nostalgický nápad, který se používá dodnes: stavové LED diody ukazovaly, zda se z paměti čte nebo do ní zapisuje. Měl být použit ve spojení se vstupní LED, kterou jsem již měl. Vstupní LED byla připojena ke generátoru signálu /WAIT, aby nám naznačila, že systém čeká na vstup (já se tam dostanu, nebojte se). Uvažoval jsem o přidání LED diody pro indikaci zápisu IO, ale došel jsem k závěru, že změna výstupních LED už bude skvělým indikátorem. Když o tom přemýšlím, možná to ještě přidám. Přesto považuji za užitečné vědět, zda se paměť čte nebo zapisuje. Každopádně je to užitečné pro ladění programu. Ve skutečnosti jsem to ve velké míře používal, když jsem se pokoušel dostat svůj program do provozu: „proč to zapisuje do paměti? To se zatím dělat nemá!"

n

K ovládání těchto LED jsem použil quad NOR gate. Použil jsem všechny brány. Ke generování stavových signálů byly použity pouze dva, ale čip nemá schopnosti napájet LED diody. Jsou schopné potopit tolik energie, takže jsem použil další dvě brány NOR jako invertory a připojil LED diody jako takové. Protože jedna LED slouží k indikaci čtení a druhá pro zápis a požadavek na čtení a zápis nenastane současně, dokázal jsem se zbavit použití pouze jednoho rezistoru pro obě LED diody. Pokud jde o signály, které jsem potřeboval dekódovat, bylo to také dost snadné. Chtěl jsem, aby byly indikovány všechny požadavky na čtení paměti, takže první brána NOR měla na svých vstupech /MREQ a /RD. Stav zápisu byl trochu složitější, ale stejně snadný. Stále jsem používal /MREQ jako jeden vstup, ale použití /WR jako druhého by způsobilo malou nuanci, které jsem se chtěl vyhnout. Ukázalo by to VŠECHNY požadavky na zápis. Chtěl jsem jen ty, které ve skutečnosti prošly. Jak bych to tedy udělal? Pamatujete si, jak mám systém nastavený, aby bylo možné zapisovat pouze RAM? Jako další vstup do brány NOR jsem použil RAM /CE. To znamená, že LED dioda se rozsvítí pouze tehdy, když je vybrána paměť RAM a probíhá požadavek na zápis. Pokud jde o barvu LED, vybral jsem jako indikátor čtení oranžovou (ale našel jsem jen žluté) a červenou jako indikátor zápisu.

Krok 4: Vstup a výstup

V předchozím kroku jste si možná všimli, že jsem na desku již přidal některé ze zbývajících komponent. Rezervoval jsem si prostor, abych omylem neumístil dráty tam, kde jsem chtěl součástku (takže bych pro tuto součástku musel najít nové umístění). Možná jste si také všimli, že jsem nechal vstupní spínače na místě a zapojil je až k napájecí liště. Rozhodl jsem se, že původní místo je dokonalým místem, a rozhodl jsem se umístit výstupní LED diody poblíž (výše). Vpravo od pruhové obrazovky je vstupní západka. Nad tím je výstupní západka a nalevo od ní je ovladač LED. Začal jsem připojením displeje k ovladači, protože to bylo nejjednodušší. Poté jsem připojil přepínače na vstupní stranu vstupní západky. Dále jsem připojil výstupní stranu výstupní západky k ovladači LED. Může se to zdát jako trapný příkaz k jejich zapojení, ale mělo to svůj důvod. Vstup výstupní západky měl být připojen k datové sběrnici stejně jako výstup vstupní západky. Cílem bylo připojit výstupy vstupní západky ke vstupům výstupní západky, což jsem udělal. Pak už jsem jen musel dostat ten nepořádek připojený k datové sběrnici. Nezáleželo na tom, kam tato spojení fyzicky vedla, protože by byla všechna elektricky propojena. Počítač je nyní téměř hotový.

Krok 5: Reset a dokončení vstupu a výstupu

Litujeme, pro tento krok nejsou žádné obrázky. Obrázky najdete v předchozím kroku.

n

Možná jste si na posledním obrázku předchozího kroku všimli, měl jsem nainstalované zelené tlačítko a další logický čip. Čip je brána NEBO. Ke generování signálu /WAIT se používají dvě brány. Jeden generuje signál pomocí OR-ing /IORQ a /RD z procesoru. Výstup je přiveden do druhé brány, kde se opět dostane OR’d k tlačítku. Tlačítko přináší vstup brány vysoko, čímž se výstup zvýší vysoko. Tento výstup je přiveden na pin procesoru /WAIT. Zatímco není stisknut, odpor drží vstup nízko. Zpočátku jsem používal odpor 10K, ale LS32 ve skutečnosti uváděl na vstup napětí. Rezistor ji nespustil dostatečně nízko a musel jsem ji vyměnit za 1K. Každopádně jde o to, že když je vznesen požadavek na čtení IO, první a druhá brána NEBO řekne procesoru, aby počkal. Jakmile nastavíte přepínače vstupu na cokoli chcete, stisknete tlačítko a vyvede procesor z čekací podmínky. Zelená LED „vstupu“, jak jsem tomu říkal v předchozím kroku, je zapojena tak, že když kolík /WAIT zhasne, rozsvítí se.

n

Ale ještě jsme neskončili. Vstupní klopný obvod potřebuje signál, aby věděl, kdy je vstup dat platný, a měl by být vložen do procesoru. Tento hodinový kolík je aktivní vysoko. Dříve jsme jej připojili k tlačítku. Toto je stále platná možnost, ale tentokrát jsem se rozhodl dát to na stejný výstup jako druhá brána OR. Tento IC má také pin /OE, který je třeba řídit. Pokud by byla držena vysoko, nikdy by nevkládala data do sběrnice. Pokud by se držel nízko, vždy by řídil autobus. Abych to vyřešil, jednoduše jsem použil třetí bránu OR. Vstupy jsou /IORQ a /RD a výstup jde přímo do /OE západky.

n

Výstupní západka také potřebuje, aby byl poháněn hodinový kolík. Opět je aktivní vysoko. Ve svém schématu jsem nakreslil čtvrtou bránu OR přímo pohánějící pin pomocí /IORQ a /WR. To znamenalo, že hodinový kolík bude držen vysoko, dokud nebude podán požadavek na zápis, pak půjde dolů a potom znovu vysoko. To by pravděpodobně bylo v pořádku, protože na datové sběrnici by byla stále platná data bezprostředně po pokusu o zápis, ale z technického hlediska to byl nesmysl. Této chyby jsem si všiml až poté, co jsem pořídil poslední obrázky, ale roztrhl jsem toto připojení a poté jsem z logiky řízení paměti přivedl výstup brány OR do jednoho z nepoužívaných měničů a poté připojil jeho výstup k hodinovému kolíku. Také jsem opravil schéma a našel další chybu, kterou jsem udělal. Také jsem to opravil.

n

Když jsem to všechno konečně udělal, měl jsem velmi malé množství práce: resetovací obvod. Přidal jsem tlačítko na desku a pomocí 10K rezistoru držel jednu stranu vysoko. Druhá strana jde přímo na zem. Druhou stranou, kterou drží vysoko, je výstup /RESET, který šel na každý čip pinem /RESET (západka CPU a výstupu). Aby bylo možné provést reset při zapnutí, přidal jsem na výstup /RESET kondenzátor. Myšlenka je taková, že rezistor s velkou hodnotou by způsobil, že relativně velký kondenzátor se bude nabíjet pomalu a držet piny /RESET nízko po určitý počet hodinových cyklů (CPU potřebuje čtyři taktovací cykly). Už asi tušíte, jaká je negativní stránka tohoto obvodu. Je to stejný zápor jako předchozí verze, protože je to stejný obvod. Když je tlačítko stisknuto, kondenzátor je v podstatě zkratován tlačítkem. To je špatné jak pro čepici, tak pro tlačítko, takže pokud chcete, aby byla vaše sestava trochu trvalejší, možná ji budete chtít předělat. Myslel jsem na další časovač 555 nastavený v monostabilním režimu. Ale tím je obvod počítače nyní dokončen. Jé. Nyní to potřebuje naprogramovat.

Krok 6: Programování

Programování této věci bylo noční můrou. Postavil jsem programátor Arduino EEPROM. Nefungovalo to. Postavil jsem další na základě designu a kódování někoho jiného. Stále nefungovalo. Vrátil jsem se k osvědčené metodě ručního nastavení adres a datových bytů. Nějak jsem to popletl. Zkusil jsem to znovu a stále jsem to špatně pochopil. Vrátil jsem se ještě jednou a zjistil, že je vypnutý o jediný bajt, tak jsem to opravil a nakonec to díky bohu fungovalo.

n

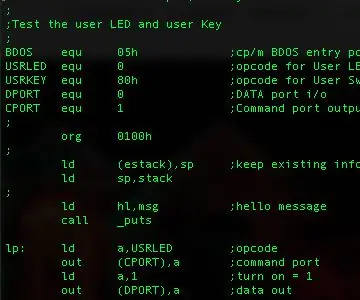

Pokud jde o skutečný program, vypadá to, že je super složitý a těžko sledovatelný, ale není. Je to vlastně docela jednoduché. Polovina kopíruje čísla kolem. Druhá polovina je rozdělena mezi 16bitovou matematiku, podmíněné skoky a ještě více kopírovacích čísel kolem. Dovolte mi to projít a říct vám, jak to funguje.

n

Inicializace pouze nastaví některé hodnoty registru pro použití programem. Programová smyčka je o něco složitější, ale ne celá. Nejprve přijímá vstup do registru A na portu 00. Poté se registr E zapíše do paměti. V prvních dvou smyčkách registr E obsahuje nevyžádaná data, takže se ho pokoušíme zapsat do posledních dvou bytů prostoru ROM, protože ve skutečnosti nebude zapsán; ukazatel adresy (IY) se poté zvýší. Hodnota uložená v D se poté přesune do E, aby byla zapsána jako další. A se pak načte do D a L a E se zkopíruje do H. HL je místo, kde probíhá porovnávání hodnot odečtením a kontrolou ZF (nulový příznak). První porovnávaná hodnota je uložena v registrech B a C. B a C jsou považovány za jeden 16bitový registr BC. Pokud jsou hodnoty stejné, program skočí přímo do prostoru RAM, kde se předpokládá, že se nachází uživatelský kód. Pokud kód v BC není shodný, pak se HL načte s počátečními hodnotami z D a E a znovu se porovná s hodnotou v SP stejným způsobem, jakým byl srovnáván s BC. Pokud je to shoda, má stejný výsledek, ale do paměti jsou zapsány tři další bajty. Bajty jsou kód, který způsobí, že CPU přeskočí zpět na úplný začátek programu (reset softwaru). Pokud však druhé srovnání neodpovídalo, program se vrátí na místo, kde získá hodnotu od uživatele.

n

LD SP, EDBFH; exe kód (přidává skok)

n

LD IY, FFEH; počáteční ukazatel paměti pro ukládání kódu

n

LD BC, EDC3H; exe kód (bez smyčky)

n

smyčka; direktiva assembleru, takže nemusíme vědět, kde v paměti je tato část

n

IN A, (00H); získat programová data

n

LD (IY+00H), E; E obsahuje kód, který se má uložit

n

INC IY; přesunout na další místo v paměti

n

LD E, D; ld D do E

n

LD D, A; ld A do D

n

LD H, E; ld E do H

n

LD L, D; ld D do L

n

NEBO A; resetovat vlajku přenosu

n

SBC HL, BC; vrací 0, pokud byl zadán exe kód 2

n

JP Z, 1000H; pokud ano, přejděte na a spusťte program

n

LD H, E; jinak je aktualizujte na správné hodnoty

n

LD L, D

n

NEBO A; první odčítání může mít nastavený příznak přenosu. Vymažte to

n

SBC HL, SP; vrací 0, pokud byl zadán exe kód 1

n

JP NZ, smyčka; pokud ne, opakujte postup (počínaje získáním hodnoty)

n

LD (IY+00H), C3H; v opačném případě vložte skokový kód na konec uživatelského programu

n

LD (IY+01H), 00H; jump v zásadě funguje jako reset softwaru

n

LD (IY+02H), 00H; je to úplný reset v případě, že došlo k úpravě registrů

n

JP 1000H; skočit na a spustit uživatelský program

Doporučuje:

Sestavení počítače 1 2. zasedání KCTC: 14 kroků

Sestavení počítače 1 2. zasedání KCTC: K dokončení sestavení budete potřebovat následující součásti: 1) základní deska 2) procesor 3) chladič + ventilátor 4) RAM5) počítačová skříň 6) pevný disk 7) napájecí zdroj 8) grafická karta

Jak vyrobit osobní mini stolní ventilátor ze starého počítače - vejde se do kapsy: 6 kroků

Jak vyrobit osobní mini stolní ventilátor ze starého počítače - vejde se do kapsy: Ukážu vám, jak ze starého počítače vyrobit osobní mini stolní ventilátor. Bonusem je, že se dokonce vejde do kapsy. Jedná se o velmi jednoduchý projekt, takže není potřeba mnoho zkušeností ani odborných znalostí. Začněme tedy

Z80-mbc2 Z80 Code Flash Uživatelská LED: 3 kroky

Z80-mbc2 Z80 Code Flash User LED: Toto je příklad uživatelského LED programu napsaného v assembleru Z80 pro počítač z80-mbc2. Udělal jsem to pro mě testovací a revizní cvičení, toto je můj první program Z80 za více než 35 let. Užijte si to

Sestavení počítače: 5 kroků

Sestavení PC: Dnes budete stavět svůj vlastní počítač. Budete potřebovat tyto komponenty: Základní deska RAM CPU, tepelná synchronizace, pevný disk nebo SSD napájecí zdroj, ventilátory, GPU, Existuje mnoho výhod při stavbě vlastního počítače, jako je levnější

Jak odesílat velké soubory z počítače do počítače: 6 kroků

Jak odesílat velké soubory z počítače do počítače: S postupujícím technologickým vývojem se velikost souborů stále zvyšuje. Pokud se věnujete kreativnímu řemeslu, jako je návrh nebo modelování, nebo jen fandíte, může být přenos velkých souborů obtížný. Většina e -mailových služeb omezuje maximální velikost přílohy na přibližně 25